Altera Video and Image Processing Suite User Manual

Page 179

Signal

Direction

Description

write_master_av_write

Output

write_master

port Avalon-MM

write

signal. The IP core

asserts this signal to indicate write requests from the

master to the system interconnect fabric.

write_master_av_writedata

Output

write_master

port Avalon-MM

writedata

bus. These

output lines carry data for write transfers.

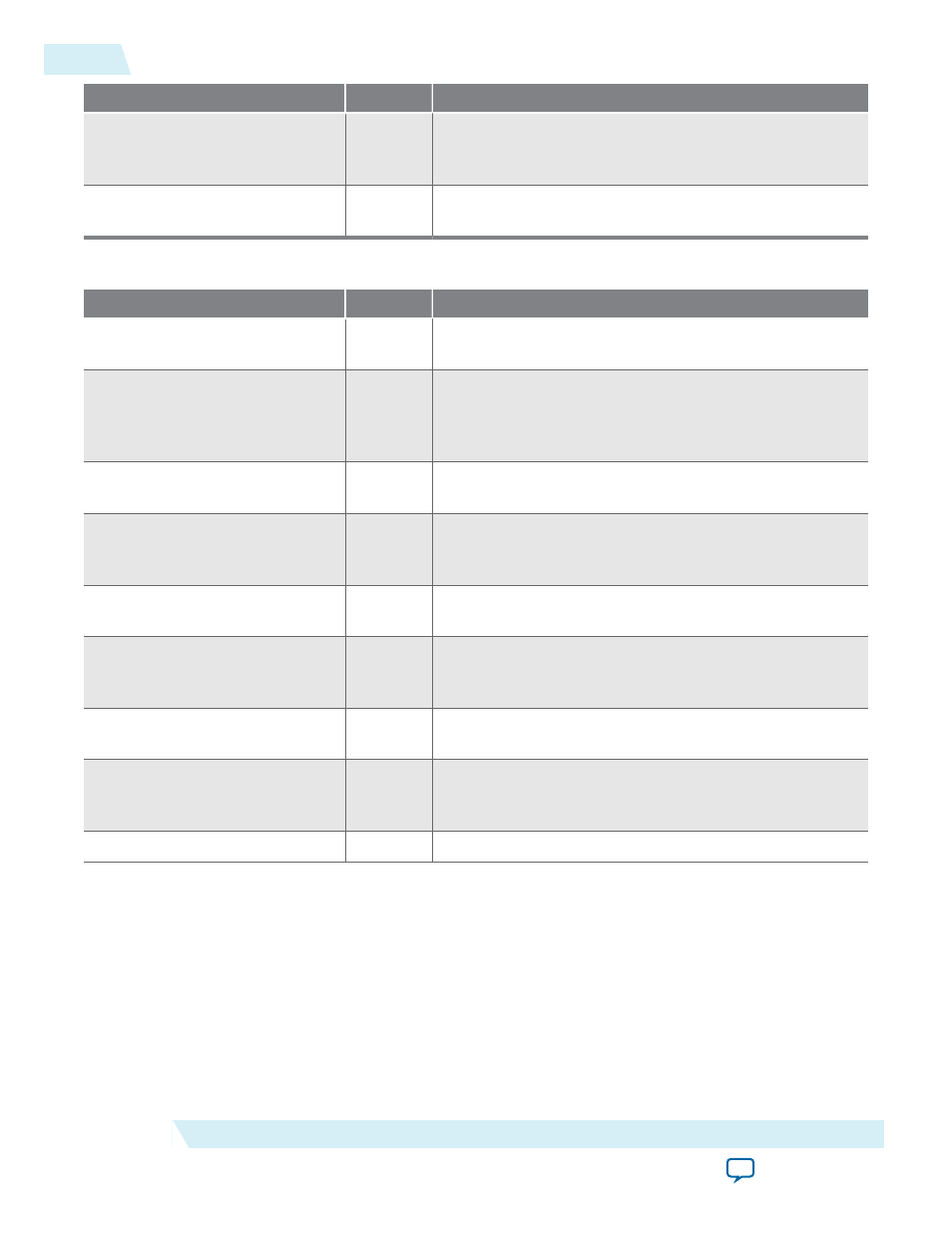

Table 12-7: Signals for Deinterlacer II and Broadcast Deinterlacer IP Cores

Signal

Direction

Description

av_mm_clock

Input

Clock for the Avalon-MM interfaces. The interfaces

operate on the rising edge of this signal.

av_mm_reset

Input

Reset for the Avalon-MM interfaces. The interfaces

asynchronously reset when you assert this signal. You

must deassert this signal synchronously to the rising edge

of the

av_mm_clock

signal.

control_address

Input

control

slave port Avalon-MM

address

bus. This bus

specifies a word offset into the slave address space.

control_write

Input

control

slave port Avalon-MM

write

signal. When you

assert this signal, the

control

port accepts new data from

the

writedata

bus.

control_writedata

Input

control

slave port Avalon-MM

writedata

bus. The IP

core uses these input lines for write transfers.

control_read

Output

control

slave port Avalon-MM

read

signal. When you

assert this signal, the control port produces new data at

readdata

.

control_readdata

Output

control

slave port Avalon-MM

readdatavalid

bus. The

IP core uses these output lines for read transfers.

control_readdatavalid

Output

control

slave port Avalon-MM

readdata

bus. The IP

core asserts this signal when the

readdata

bus contains

valid data in response to the read signal.

control_waitrequest

Output

control

slave port Avalon-MM

waitrequest

signal.

12-20

Deinterlacing Signals

UG-VIPSUITE

2015.05.04

Altera Corporation

Deinterlacing IP Cores