Altera Video and Image Processing Suite User Manual

Page 266

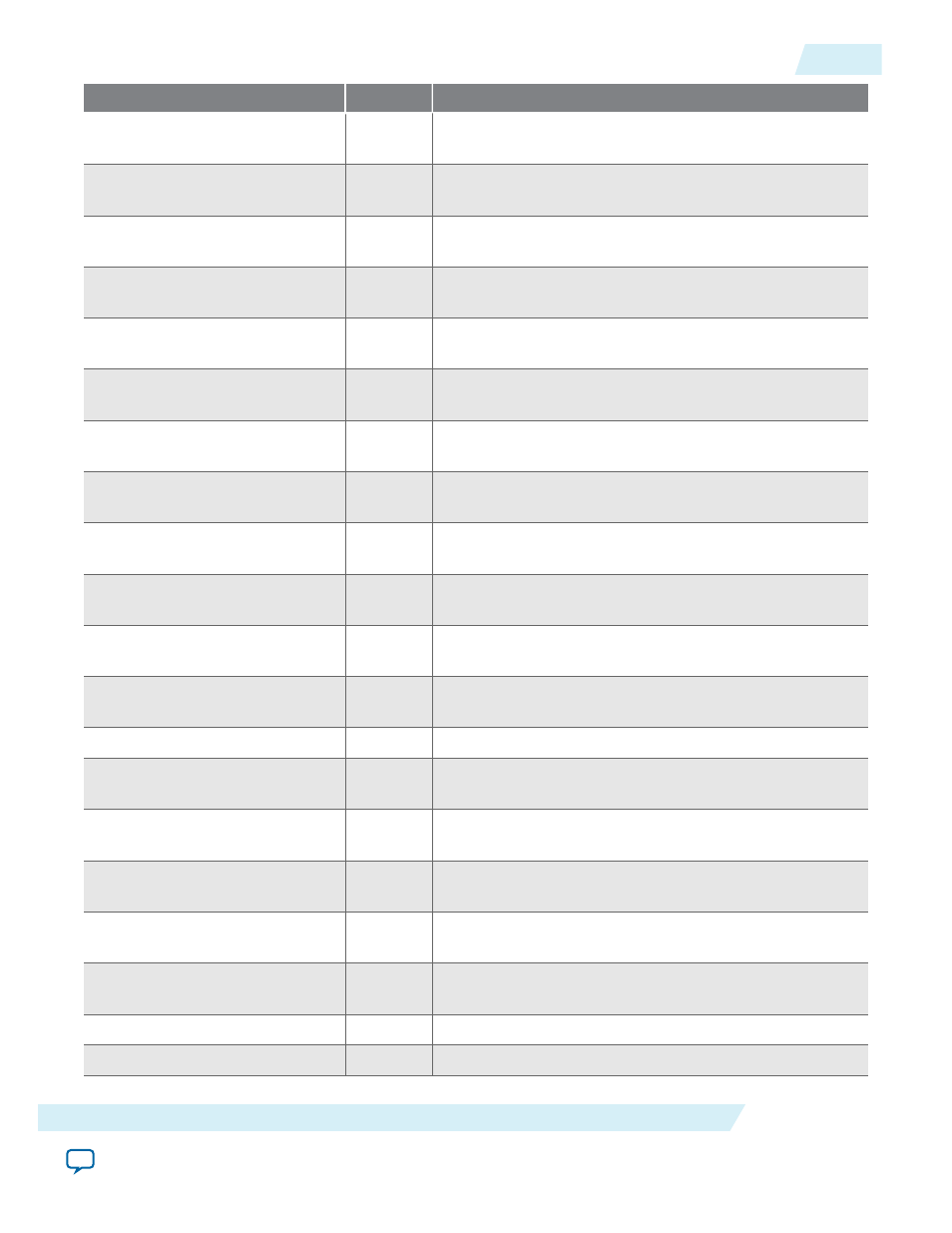

Signal

Direction

Description

din_data

Input

din

port Avalon-ST

data

bus. This bus enables the

transfer of pixel data into the IP core.

din_endofpacket

Input

din

port Avalon-ST

endofpacket

signal. This signal

marks the end of an Avalon-ST packet.

din_ready

Output

din

port Avalon-ST

ready

signal. This signal indicates

when the IP core is ready to receive data.

din_startofpacket

Input

din

port Avalon-ST

startofpacket

signal. This signal

marks the start of an Avalon-ST packet.

din_valid

Input

din

port Avalon-ST

valid

signal. This signal identifies the

cycles when the port must enter data.

dout_data

Output

dout

port Avalon-ST

data

bus. This bus enables the

transfer of pixel data out of the IP core.

dout_endofpacket

Output

dout

port Avalon-ST

endofpacket

signal. This signal

marks the end of an Avalon-ST packet.

dout_ready

Input

dout

port Avalon-ST

ready

signal. The downstream

device asserts this signal when it is able to receive data.

dout_startofpacket

Output

dout

port Avalon-ST

startofpacket

signal. This signal

marks the start of an Avalon-ST packet.

dout_valid

Output

dout

port Avalon-ST

valid

signal. The IP core asserts this

signal when it produces data.

capture_data

Output

capture

port Avalon-ST

data

bus. This bus enables the

transfer of data out of the IP core.

capture_endofpacket

Output

capture

port Avalon-ST

endofpacket

signal. This signal

marks the end of an Avalon-ST packet.

capture_empty

Output

capture

port Avalon-ST

empty

signal.

capture_ready

Input

capture

port Avalon-ST

ready

signal. The downstream

device asserts this signal when it is able to receive data.

capture_startofpacket

Output

capture

port Avalon-ST

startofpacket

signal. This

signal marks the start of an Avalon-ST packet.

capture_valid

Output

capture

port Avalon-ST

valid

signal. The IP core asserts

this signal when it produces data.

control_address

Input

control

slave port Avalon-MM

address

bus. This bus

specifies a byte address in the Avalon-MM address space.

control_burstcount

Input

control

slave port Avalon-MM

burstcount

signal. This

signal specifies the number of transfers in each burst.

control_byteenable

Input

control

slave port Avalon-MM

byteenable

bus.

control_debugaccess

Input

control

slave port Avalon-MM

debugaccess

signal.

UG-VIPSUITE

2015.05.04

Avalon-ST Video Monitor Signals

21-5

Avalon-ST Video Monitor IP Core

Altera Corporation