Video clipping control registers, Video clipping control registers -6 – Altera Video and Image Processing Suite User Manual

Page 132

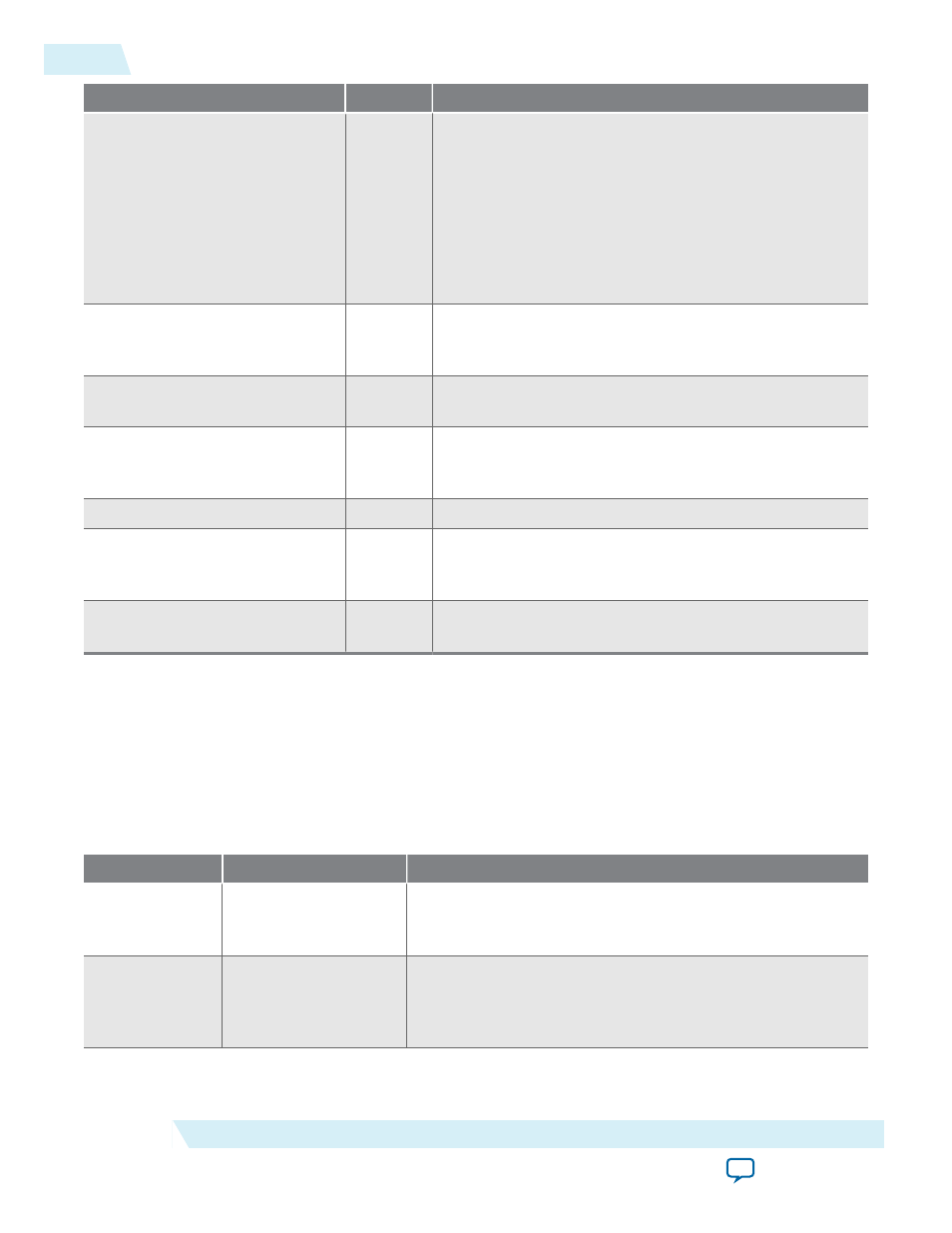

Signal

Direction

Description

control_byteenable

Input

control

slave port Avalon-MM

byteenable

bus. This bus

enables specific byte lane or lanes during transfers. Each

bit in

byteenable

corresponds to a byte in

writedata

and

readdata

.

During writes,

byteenable

specifies which bytes are being

written to; other bytes are ignored by the slave. Slaves that

simply return

readdata

with no side effects are free to

ignore

byteenable

during reads.

control_read

Output

control

slave port Avalon-MM

read

signal. When you

assert this signal, the

control

port sends new data at

readdata

.

control_readdata

Output

control

slave port Avalon-MM

control_data

bus. The

IP core uses these output lines for read transfers.

control_readdatavalid

Output

control

slave port Avalon-MM

readdata

bus. When you

assert this signal, the control port sends new data at

control_readdata

.

control_waitrequest

Output

control

slave port Avalon-MM

waitrequest

signal.

control_write

Input

control

slave port Avalon-MM

write

signal. When you

assert this signal, the

control

port accepts new data from

the

writedata

bus.

control_writedata

Input

control

slave port Avalon-MM

writedata

bus. The IP

core uses these input lines for write transfers.

Video Clipping Control Registers

Table 8-6: Clipper Control Register Map

The control data is read once at the start of each frame and is buffered inside the IP core, so the registers can be

safely updated during the processing of a frame.

Note: All Clipper registers are write-only except at address 1.

Address

Register

Description

0

Control

Bit 0 of this register is the

Go

bit, all other bits are unused.

Setting this bit to 0 causes the IP core to stop the next time

control information is read.

1

Status

Bit 0 of this register is the

Status

bit, all other bits are unused.

The Clipper IP core sets this address to 0 between frames. It is

set to 1 while the IP core is processing data and cannot be

stopped.

8-6

Video Clipping Control Registers

UG-VIPSUITE

2015.05.04

Altera Corporation

Video Clipping IP Cores