Altera Video and Image Processing Suite User Manual

Page 25

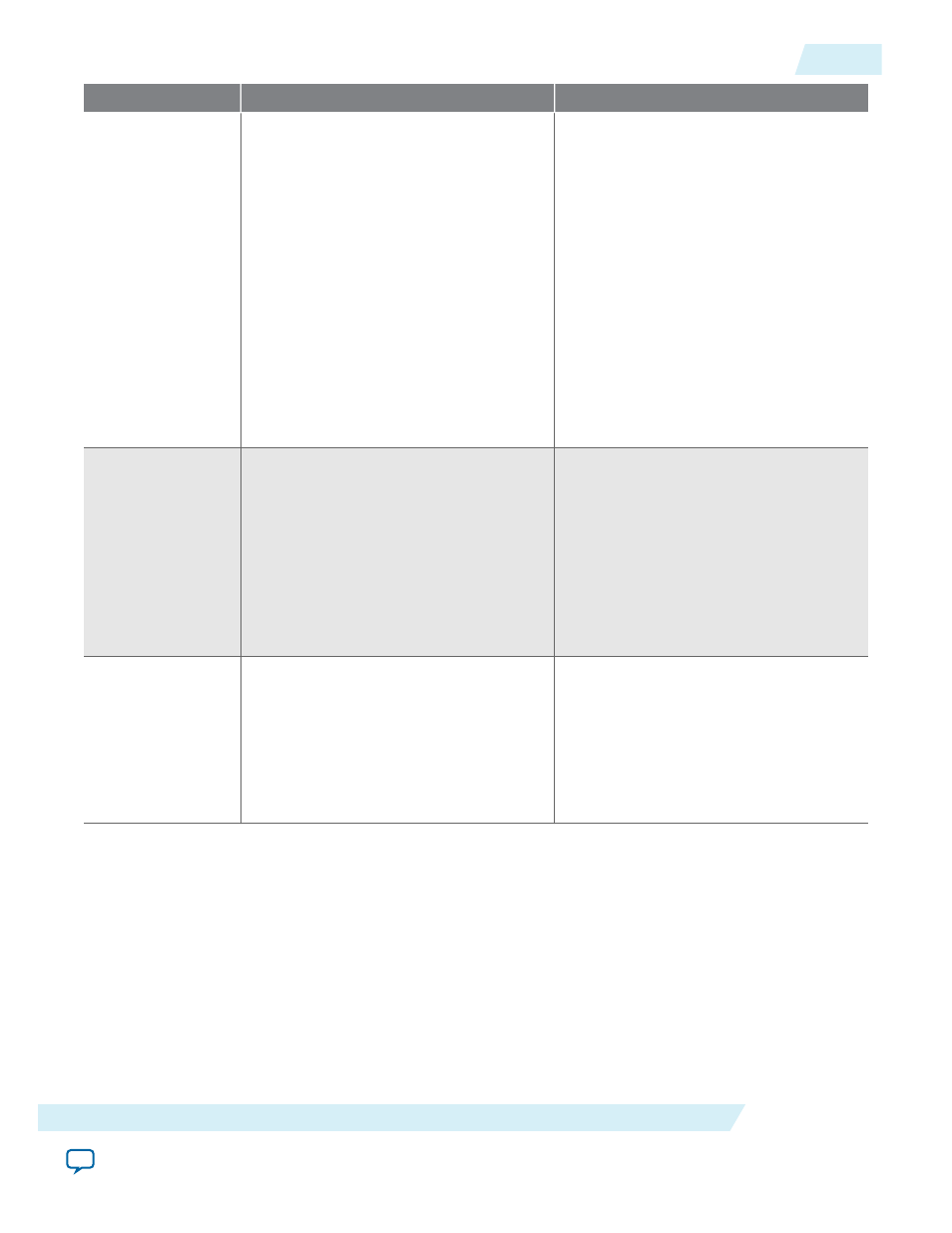

IP Core

Stall Behavior

Error Recovery

Frame Buffer/

Frame Buffer II

• May stall frequently and read or write

less than once per clock cycle during

control packet processing.

• During data processing at the input or at

the output, the stall behavior of the IP

core is largely decided by contention on

the memory bus.

• Does not rely on the content of the

control packets to determine the size

of the image data packets.

• Any early or late

endofpacket

signal

and any mismatch between the size

of the image data packet and the

content of the control packet are

propagated unchanged to the next IP

core.

• Does not write outside the memory

allocated for each non-image and

image Avalon-ST video packet—

packets are truncated if they are

larger than the maximum size

defined at compile time.

Gamma

Corrector

• Stalls only between frames and not

between rows.

• Has no internal buffering aside from the

registers of its processing pipeline— only

a few clock cycles of latency

• Processes video packets until the IP

core receives an

endofpacket

signal

—non-image packets are propagated

but the content of control packets is

ignored.

• Any mismatch of the

endofpacket

signal and the frame size is

propagated unchanged to the next IP

core.

Interlacer

• Alternates between propagating and

discarding a row from the input port

while producing an interlaced output

field—the output port is inactive every

other row.

• The delay from input to output is a few

clock cycles when pixels are propagated.

• Receiving

endofpacket

signal later

than expected—discards extra data.

• Receiving an early

endofpacket

signal—the current output field is

interrupted as soon as possible and

may be padded with a single

undefined pixel.

UG-VIPSUITE

2015.05.04

Stall Behavior and Error Recovery

1-19

Video and Image Processing Suite Overview

Altera Corporation