Altera Video and Image Processing Suite User Manual

Page 245

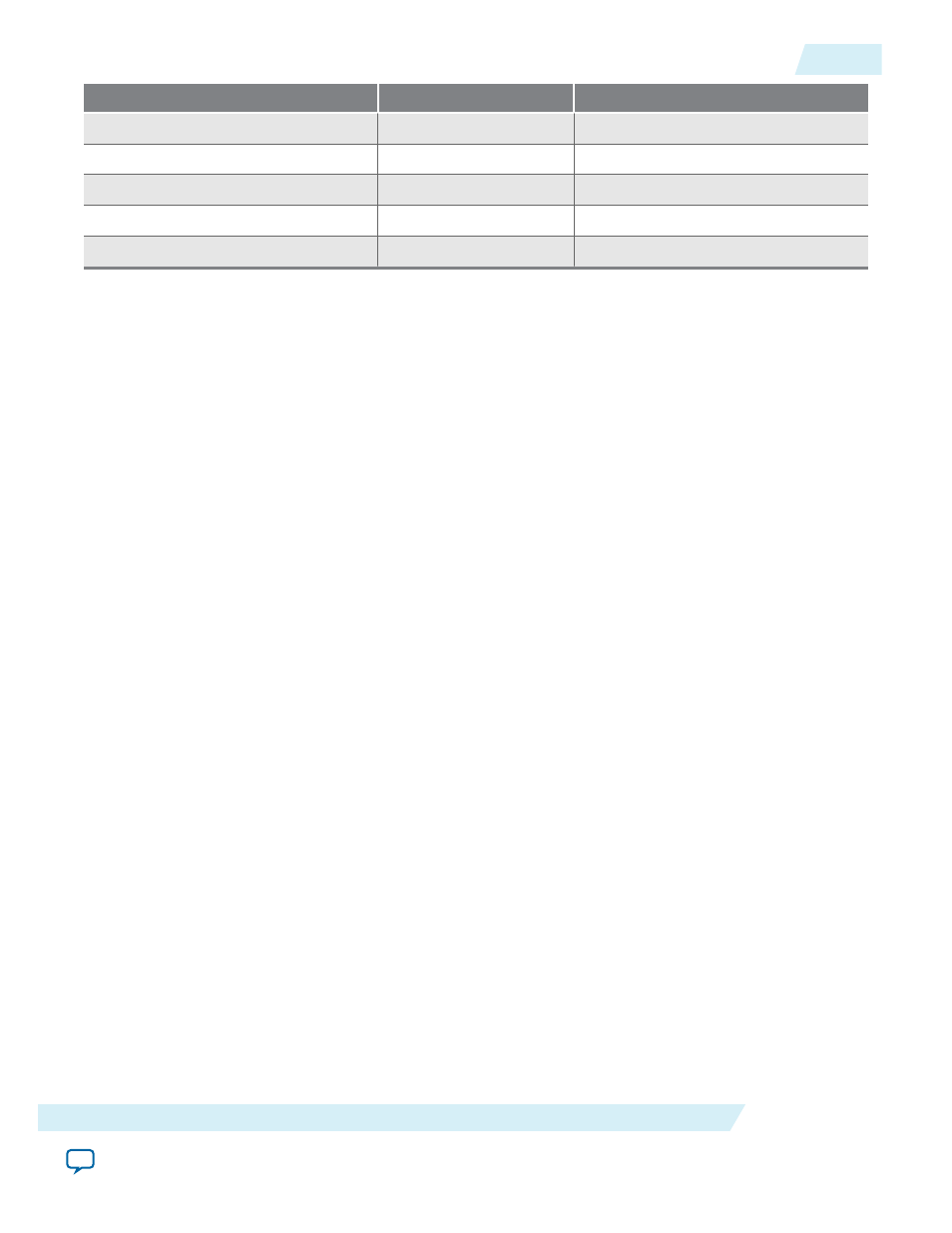

Color

R'G'B'

Y'CbCr

Green

(16,180,16)

(112,72,58)

Magenta

(180,16,180)

(84,184,198)

Red

(180,16,16)

(65,100,212)

Blue

(16,16,180)

(35,212,114)

Black

(16,16,16)

(16,128,128)

The choice of a specific resolution and subsampling for the output leads to natural constraints on the test

pattern. If the format has a horizontal subsampling period of two for the Cb and Cr components when the

output is in the Y’CbCr color space, the black borders at the left and right are two pixels wide. Similarly,

the top and bottom borders are two pixels wide when the output is vertically subsampled.

The width and the horizontal subsampling may also have an effect on the width of each color bar. When

the output is horizontally subsampled, the pixel-width of each color bar is a multiple of two. When the

width of the image (excluding the left and right borders) cannot be exactly divided by eight, then the last

black bar is larger than the others.

For example, when producing a 640×480 frame in the Y’CbCr color space with 4:2:2 subsampling, the left

and right black borders are two pixels wide each, the seven initial color bars are 78 pixels wide ((640–4)/8

truncated down to the nearest multiple of 2) and the final black color bar is 90 pixels wide (640–7×78–4).

Generation of Avalon-ST Video Control Packets and Run-Time Control

The Test Pattern Generator IP cores produce a valid Avalon-ST Video control packet before generating

each image data packet , whether it is a progressive frame or an interlaced field.

When the output is interlaced, the Test Pattern Generator IP cores produce a sequence of pairs of field,

starting with:

• F0 if the output is F1 synchronized.

• F1 if the output is F0 synchronized.

When you enable the Avalon slave run-time controller, the resolution of the output can be changed at

run-time at a frame boundary, that is, before the first field of a pair when the output is interlaced.

The Test Pattern Generator IP cores do not accept an input stream—so the Avalon-MM slave interface

pseudo-code is slightly modified:

go = 0;

while (true)

{

status = 0;

while (go != 1 )

wait();

read_control(); //Copies control to internal register

status = 1;

do once for progressive output or twice for interlaced output

{

send_control_packet();

send_image_data_header();

output_test_pattern ();

UG-VIPSUITE

2015.05.04

Generation of Avalon-ST Video Control Packets and Run-Time Control

19-3

Test Pattern Generator IP Cores

Altera Corporation