Altera Video and Image Processing Suite User Manual

Page 187

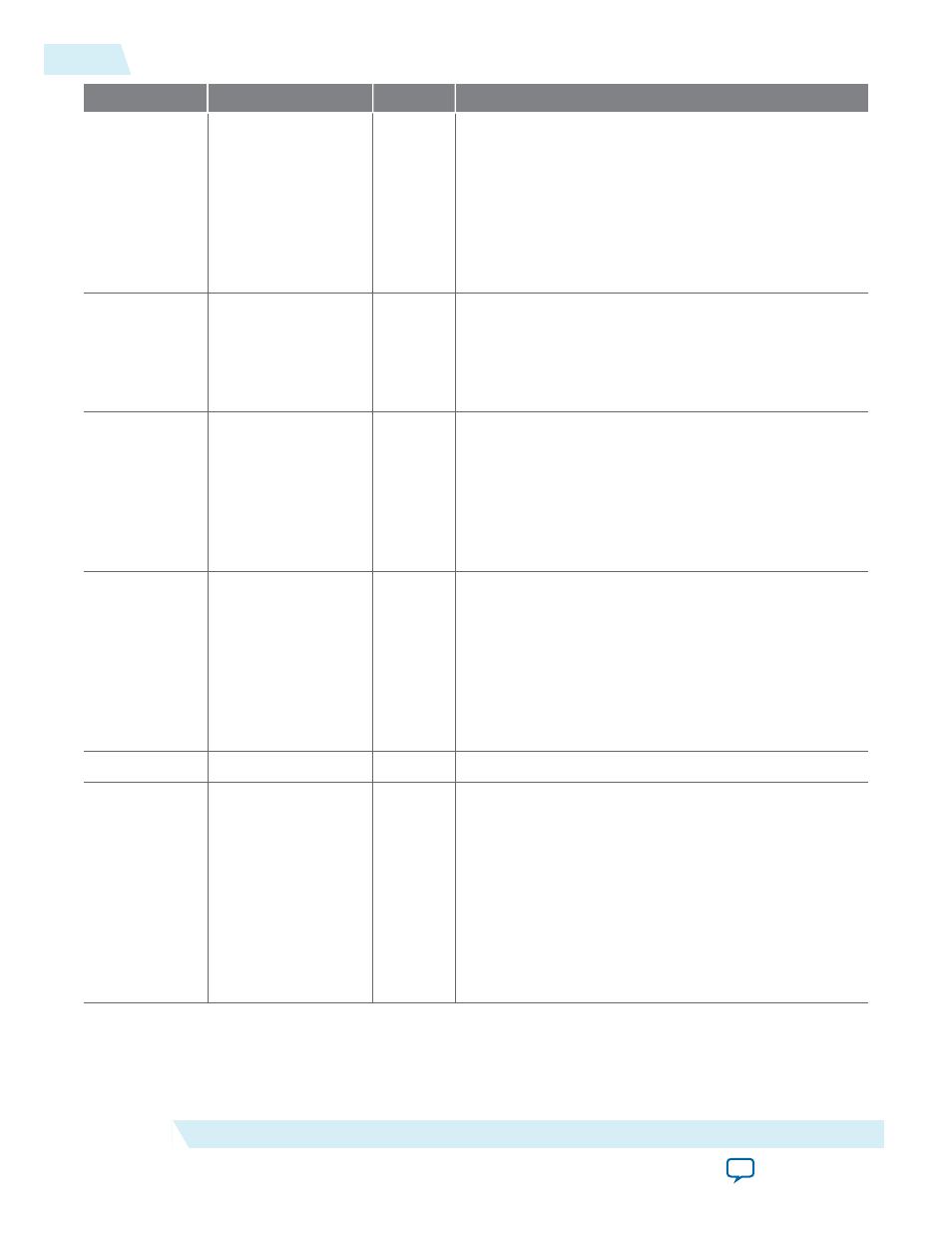

Address

Register

RO/RW

Description

16

VOF Lock Delay

RW

Specifies the number of fields elapsed after the core

detects a cadence, but before reverse telecine begins.

The delay allows for any video to drop out. If you set a

value less than five, the core locks to cadence quicker

but costs potential film artefacts.

Range: 0–31

Power on value: 5

17

Minimum Pixels

Locked

RW

Specifies the least number of pixels showing a cadence

for lock to occur.

Range: 0–(2

32

–1)

Power on value: 256

18

Min Valid SAD

Value

RW

When considering whether pixels should remain

locked, the SAD values less than this range are ignored.

Set this value high to prevent film pixels from decaying

over time if they do not show a strong 3:2 cadence.

Range: 0–255

Power on value: 1

19

Scene Change

Threshold/Bad Edit

Detection

RW

The Broadcast Deinterlacer IP core detects scene

changes or bad edits, and resets the cadence state

accordingly. The default value of 2 indicates that if

there is 2^2(4) times as much motion detected in the

next field, then a new scene or bad edit is flagged.

Range: 0–15

Power on value: 2

20

Reserved

RW

This register is reserved for future use.

21

Minimum Pixel

Kernel SAD for

Field Repeats

RW

Once a video achieves cadence lock, every pixel in the

frame will either maintain or lose lock independently

from then on. If the SAD value is less than the value for

this register, then its lock count will be incremented. If

it is higher than this value, its lock count will either

remain unchanged or be decremented (if less than min

valid SAD value).

Range: 0–255

Power on value: 80

12-28

Deinterlacing Control Registers

UG-VIPSUITE

2015.05.04

Altera Corporation

Deinterlacing IP Cores