Deinterlacing signals, Deinterlacing signals -17 – Altera Video and Image Processing Suite User Manual

Page 176

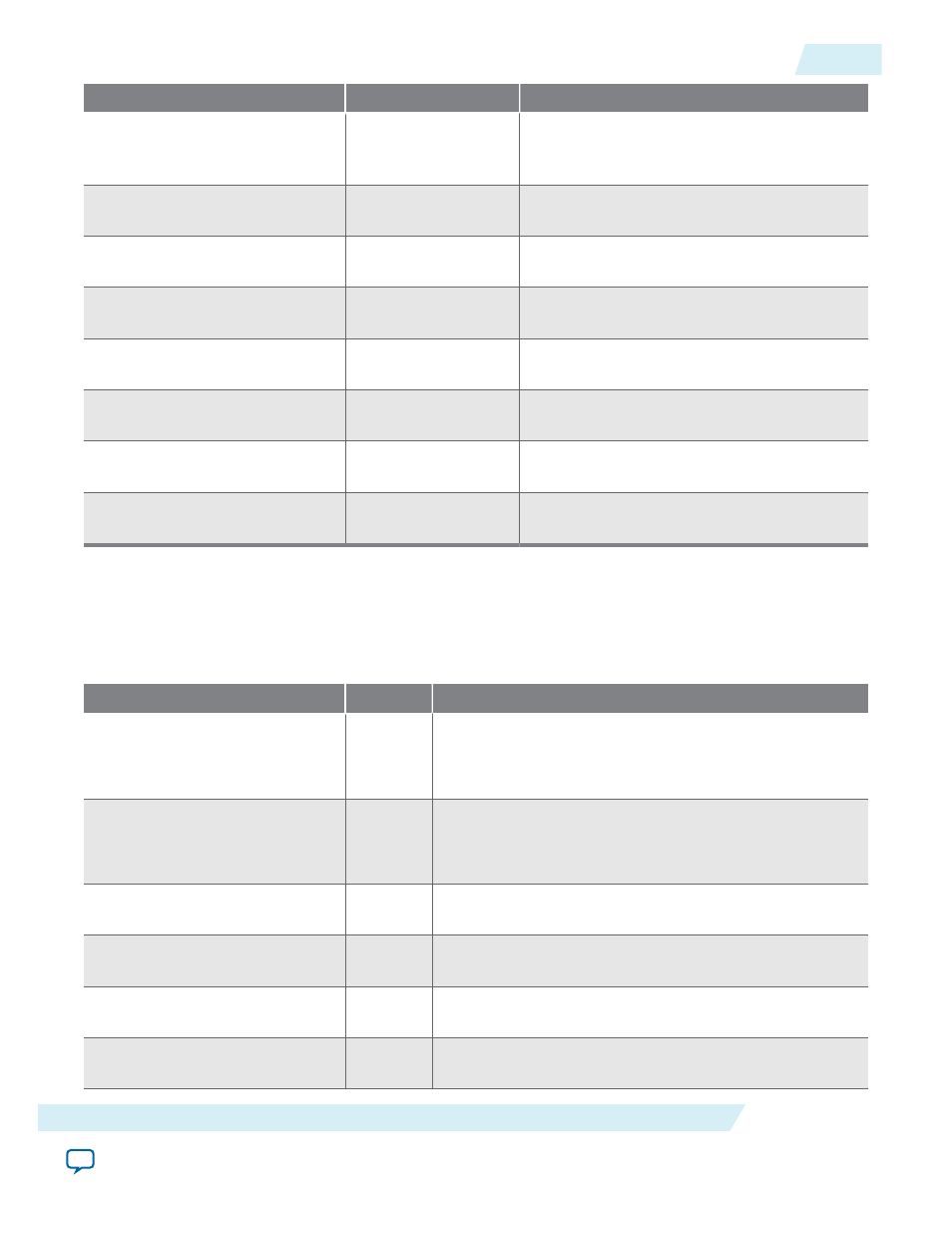

Parameter

Value

Description

EDI read master FIFO depth

8–512, Default = 64

Select the FIFO depth of the edge-dependent

interpolation (EDI) Avalon-MM read master

interface.

EDI read master FIFO burst

target

2–256, Default = 32

Select the burst target for EDI Avalon-MM

read master interface.

MA read master FIFO depth

8–512, Default = 64

Select the FIFO depth of the motion-adaptive

(MA) Avalon-MM read master interface.

MA read master FIFO burst

target

2–256, Default = 32

Select the burst target for MA Avalon-MM

read master interface.

Motion write master FIFO depth 8–512, Default = 64

Select the FIFO depth of the motion Avalon-

MM write master interface.

Motion write master FIFO burst

target

2–256, Default = 32

Select the burst target for the motion Avalon-

MM write master interface.

Motion read master FIFO depth 8–512, Default = 64

Select the FIFO depth of the motion Avalon-

MM read master interface.

Motion read master FIFO burst

target

2–256, Default = 32

Select the burst target for motion Avalon-

MM read master interface.

Deinterlacing Signals

Table 12-5: Common Signals

These signals apply to all Deinterlacing IP cores.

Signal

Direction

Description

•

clock

(Deinterlacer)

•

av_st_clock

(Deinterlacer II

and Broadcast Deinterlacer)

Input

The main system clock. The IP core operates on the rising

edge of this signal.

•

reset

(Deinterlacer)

•

av_st_reset

(Deinterlacer II

and Broadcast Deinterlacer)

Input

The IP core asynchronously resets when this signal is high.

You must deassert this signal synchronously to the rising

edge of the clock signal.

din_data

Input

din

port Avalon-ST

data

bus. This bus enables the

transfer of pixel data into the IP core.

din_endofpacket

Input

din

port Avalon-ST

endofpacket

signal. This signal

marks the end of an Avalon-ST packet.

din_ready

Output

din

port Avalon-ST

ready

signal. This signal indicates

when the IP core is ready to receive data.

din_startofpacket

Input

din

port Avalon-ST

startofpacket

signal. This signal

marks the start of an Avalon-ST packet.

UG-VIPSUITE

2015.05.04

Deinterlacing Signals

12-17

Deinterlacing IP Cores

Altera Corporation