Altera Video and Image Processing Suite User Manual

Page 151

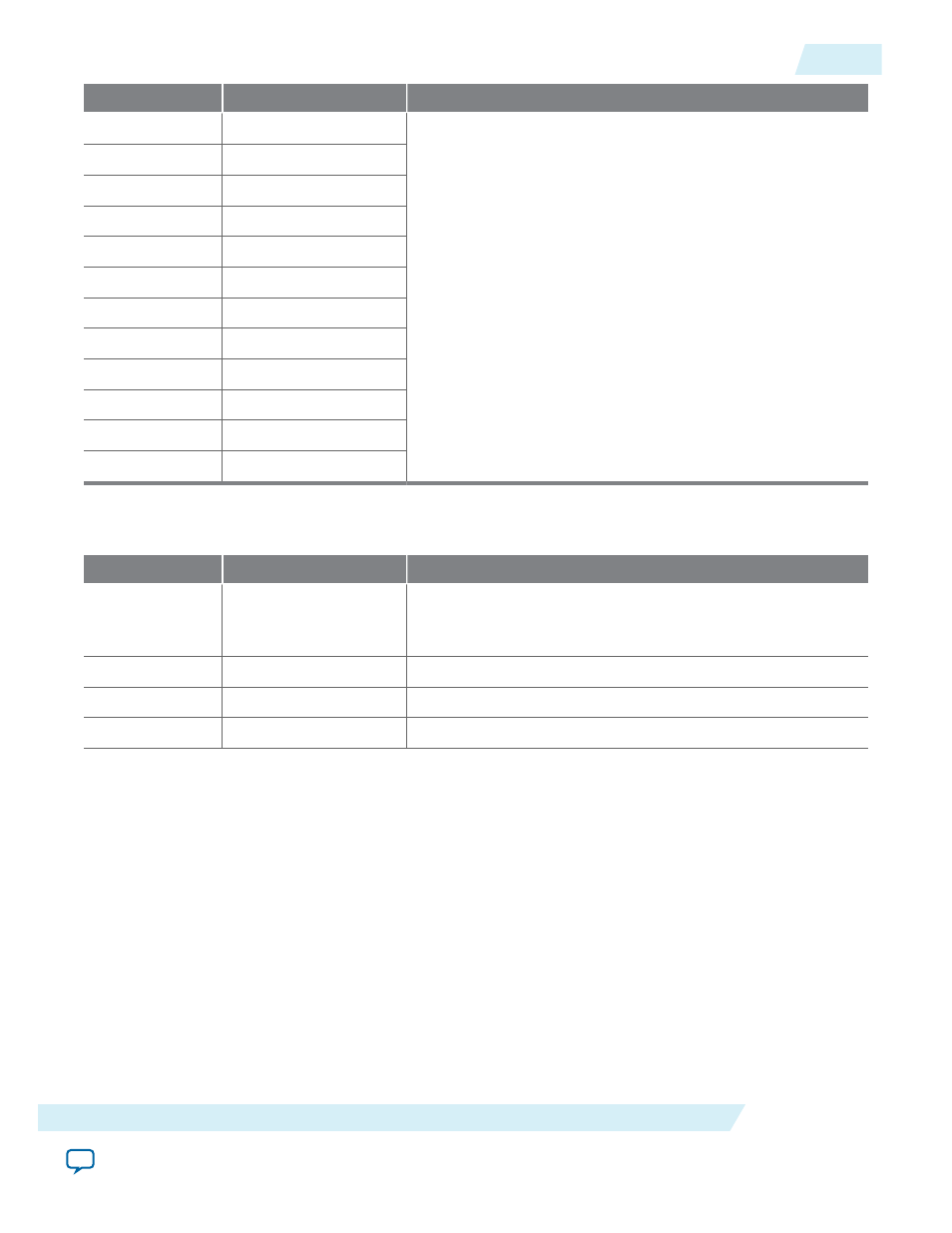

Address

Register

Description

2

Coefficient A0

The coefficient and summand registers use integer, signed 2’s

complement numbers. Refer to

on

page 10-2.

3

Coefficient B0

4

Coefficient C0

5

Coefficient A1

6

Coefficient B1

7

Coefficient C1

8

Coefficient A2

9

Coefficient B2

10

Coefficient C2

11

Summand S0

12

Summand S1

13

Summand S2

Table 10-5: Color Space Converter II Control Register

The table below describes the control register map for Color Space Converter II IP core.

Address

Register

Description

0

Control

Bit 0 of this register is the

Go

bit, all other bits are unused.

Setting this bit to 0 causes the IP core to stop the next time

control information is read.

1

Status

Bit 0 of this register is the

Status

bit, all other bits are unused.

2

Interrupts

Unused.

3

Coeff-commit

Commit mode.

UG-VIPSUITE

2015.05.04

Color Space Conversion Control Registers

10-11

Color Space Conversion IP Cores

Altera Corporation