Altera Video and Image Processing Suite User Manual

Page 186

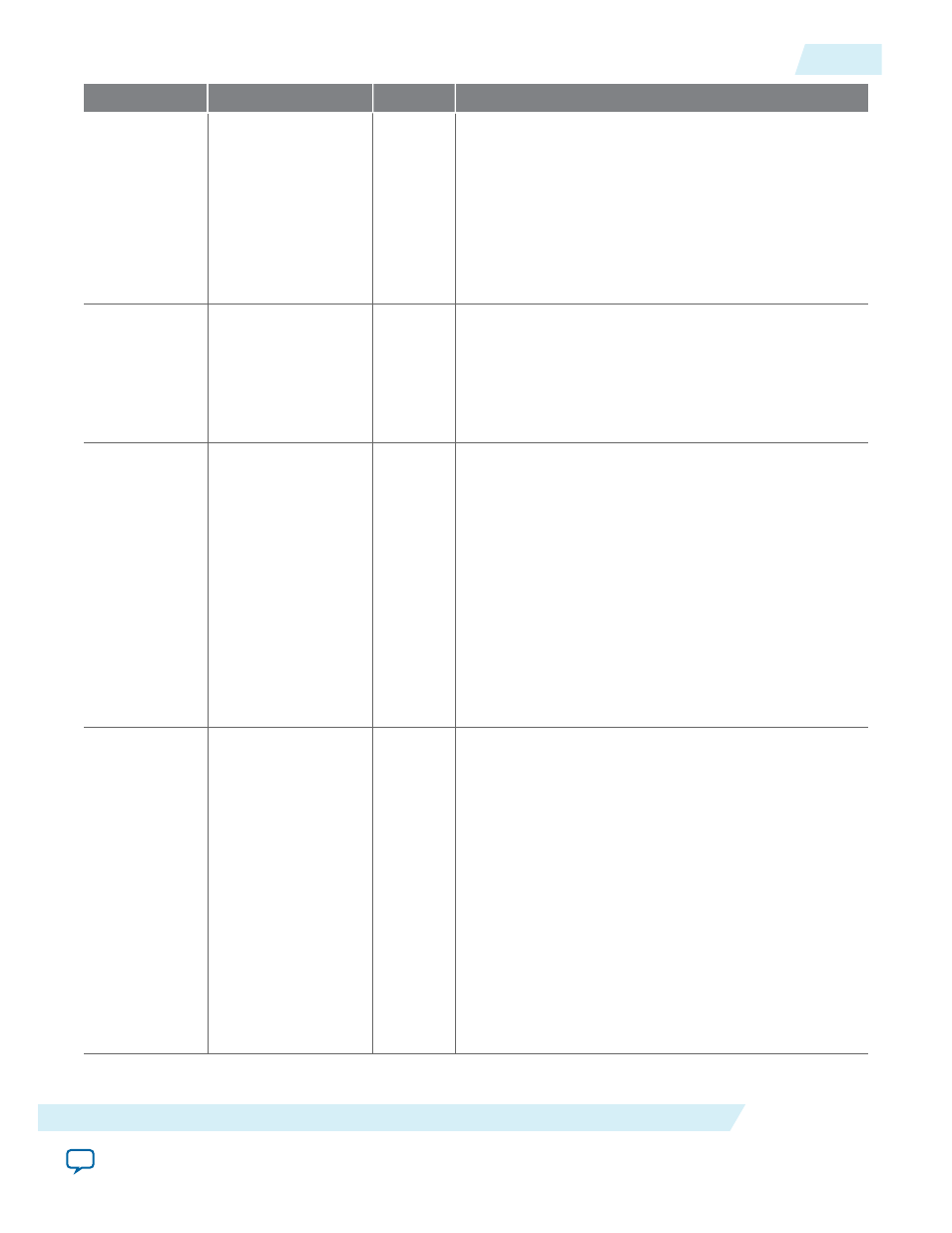

Address

Register

RO/RW

Description

12

Cadence Detect On

RW

• Setting the LSB of this register to 1 enables cadence

detection.

• Setting the LSB of this register to 0 disables cadence

detection.

• Cadence detection is disabled on reset.

Range: 0–1

Power on value: 0

13

Video Threshold

RW

The most important register to tune the video over

film features. Set lower values for more emphasis on

video and higher values for more emphasis on film.

Range: 0–255

Power on value: 160

14

Film Lock

Threshold

RW

3:2 cadence is rechecked at every 5th field.

• If a given pixel fulfils the requirements for a

cadence on a given field, the core increments its

lock count.

• If the lock count reaches the value of this register,

then the given pixel is locked.

Set lower values for greater sensitivity to cadenced

sequences. If lock is declared for a pixel, then the core

performs reverse telecine during deinterlacing.

Range: 3–7

Power on value: 3

15

Film Unlock

Threshold

RW

3:2 cadence is rechecked at every 5th field.

• If a given pixel fulfils the requirements for a

cadence on a given field, the core decrements its

lock count.

• If the lock count reaches the value of this register,

then the given pixel loses its lock.

Set lower values to cater for bad edits and poor film

qualities. The value for this register must be set lower

than the Film Lock Threshold register. The core

performs standard motion adaptive deinterlacing for

unlocked pixels.

Range: 0–5

Power on value: 0

UG-VIPSUITE

2015.05.04

Deinterlacing Control Registers

12-27

Deinterlacing IP Cores

Altera Corporation