Altera Video and Image Processing Suite User Manual

Page 23

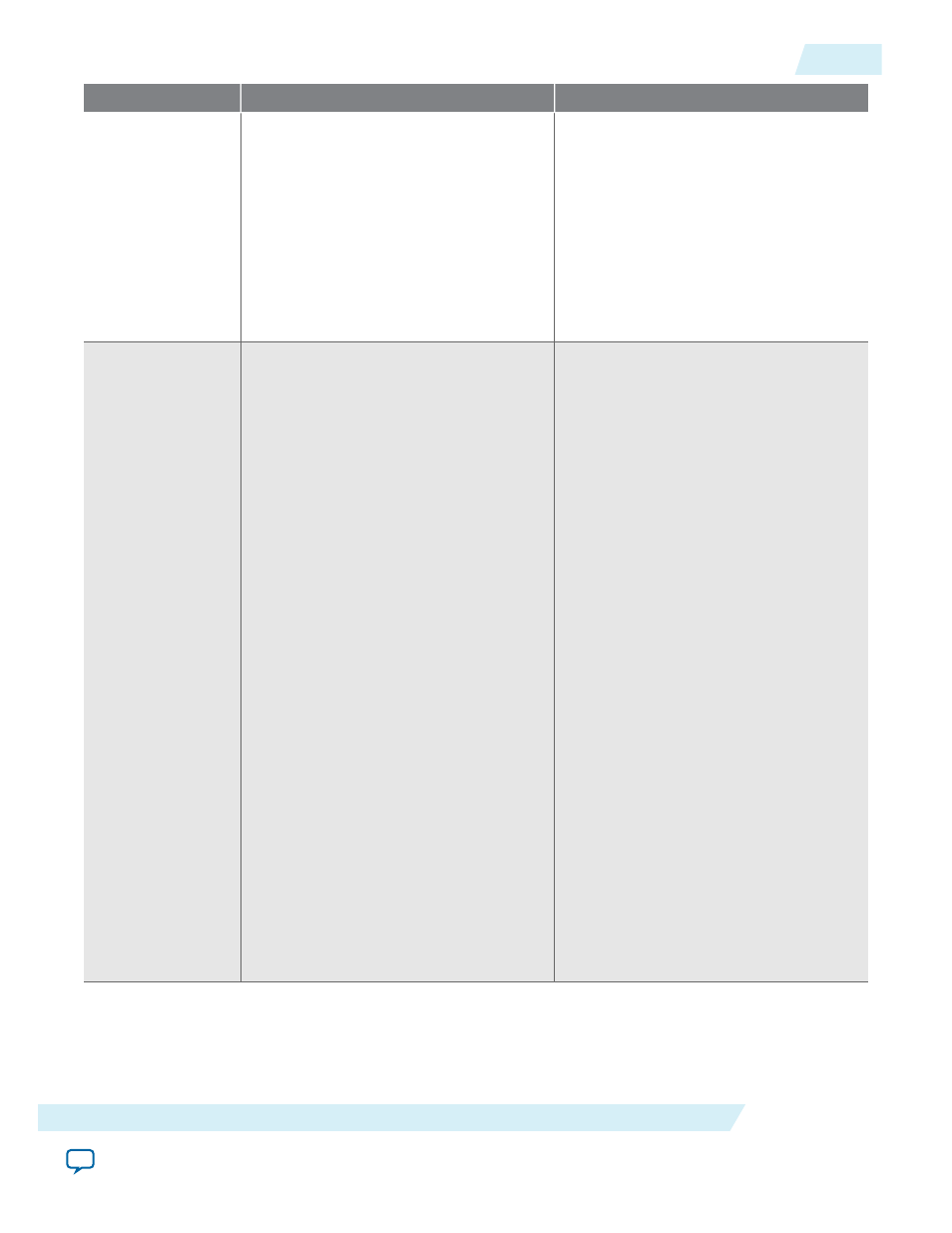

IP Core

Stall Behavior

Error Recovery

Control

Synchronizer

• Stalls for several cycles between packets.

• Stalls when it enters a triggered state

while it writes to the Avalon-MM Slave

ports of other IP cores.

• If the slaves do not provide a wait

request signal, the stall lasts for no more

than 50 clock cycles. Otherwise the stall

is of unknown length.

• Processes video packets until the IP

core receives an

endofpacket

signal

—the image width, height and

interlaced fields of the control data

packets are not compared against the

following video data packet.

• Any mismatch of the

endofpacket

signal and the frame size of video

data packet is propagated unchanged

to the next IP core.

Deinterlacer

• Bob algorithm

• While the bob algorithm (with no

buffering) is producing an output

frame, it alternates between simulta‐

neously between

• receiving a row on the input port

and producing a row of data on

the output port

• just producing a row of data on

the output port without reading

any data from the input port

The delay from input to output is just

a few clock cycles.

• While a field is being discarded, input

is read at the maximum rate and no

output is generated.

• Weave algorithm

• The IP core may stall for longer than

the usual periods between each

output row of the image.

• The delays may possibly stretch up to

45 clock cycles due to the time taken

for internal processing in between

lines.

• Motion-adaptive algorithm

• The IP core may stall up to 90 clock

cycles.

• Receiving an

endofpacket

signal too

early or too late is relative to the field

dimensions contained in the last

control packet processed.

• Receiving an

endofpacket

signal too

late—discards extra data in all

configurations.

• Receiving an early

endofpacket

signal when it is configured for no

buffering—the IP core interrupts its

processing within one or two lines

sending undefined pixels, before

propagating the

endofpacket

signal.

• Receiving an early

endofpacket

signal when it is configured to buffer

data in external memory—the input

side of the IP core stops processing

input pixels. It is then ready to

process the next frame after writing

undefined pixels for the remainder of

the current line into external RAM.

The output side of the IP core

assumes that incomplete fields have

been fully received and pads the

incomplete fields to build a frame,

using the undefined content of the

memory.

UG-VIPSUITE

2015.05.04

Stall Behavior and Error Recovery

1-17

Video and Image Processing Suite Overview

Altera Corporation