Altera Video and Image Processing Suite User Manual

Page 15

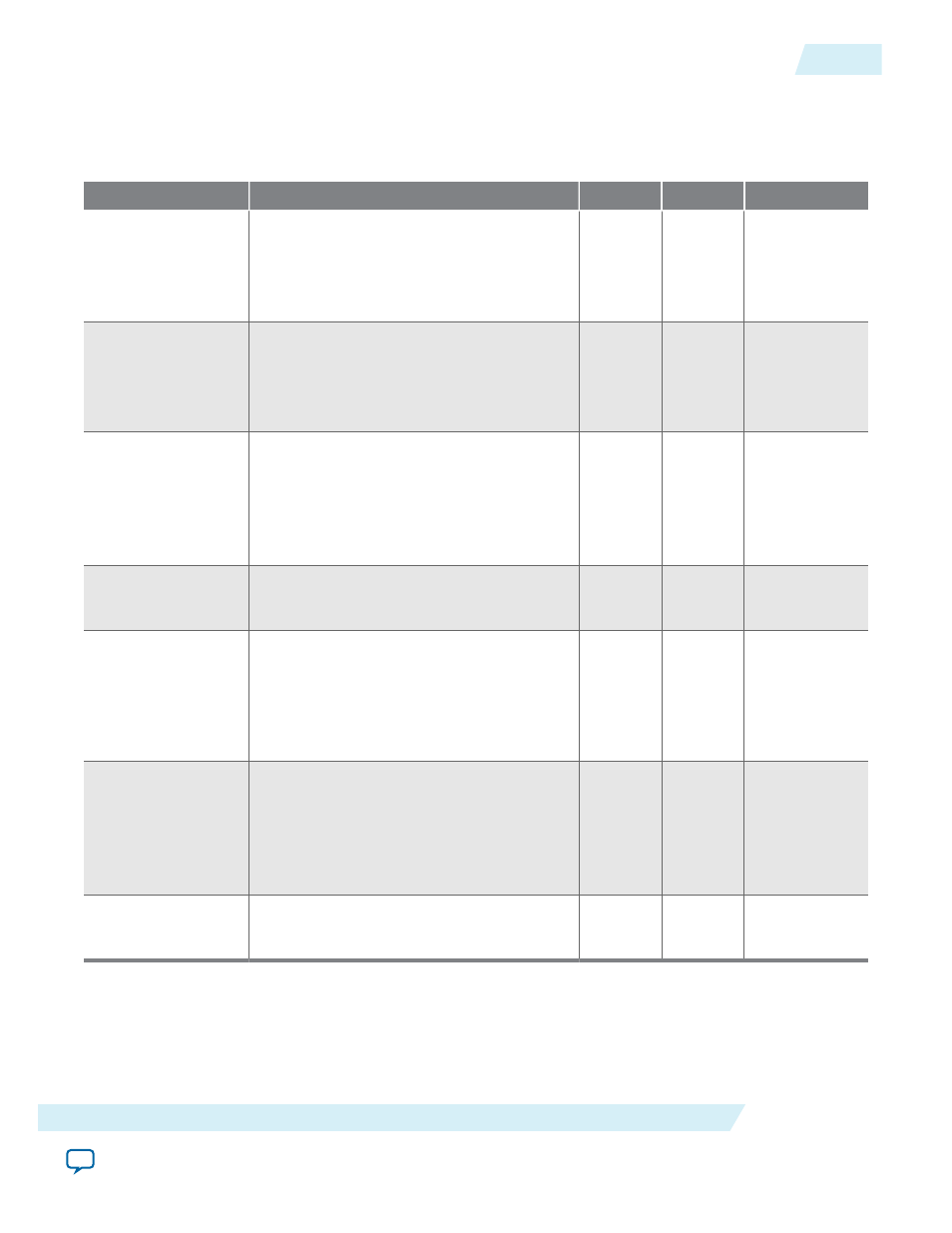

Table 1-5: Performance and Resource Data Using Arria V Devices

The following data are obtained through a 4K test design example using an Arria V device (5AGXFB3H4F35C4).

The general settings for the design is 8 bits per color plane; 2 pixels in parallel. The target f

MAX

is 148.5 MHz.

IP Core

Configuration

ALM

RAM

DSP

Mixer II

• Number of color planes in parallel = 3

• Inputs = 4

• Output = 1

• Internal Test Pattern Generator

1,591

0

0

Clocked Video

Input II

• Number of color planes in parallel = 3

• Sync signals = On separate wires

• Pixel FIFO size = 4096 pixels

• Use control port = On

540

26

0

Clocked Video

Output II

• Number of color planes in parallel = 3

• Sync signals = On separate wires

• Pixel FIFO size = 4096 pixels

• Use control port = On

• Run-time configurable video modes = 4

2,504

49

0

Color Space

Converter II

• Run-time control = On

• Color model conversion = RGb to YCbCr

1,515

0

18

Broadcast Deinter‐

lacer

• Number of color planes in parallel = 2

• Avalon-MM master local ports width =

256

• FIFO depths = 512

• Run-time control = Off

11,516

145

34

Frame Buffer II

• Number of color planes in parallel = 2

• Avalon-MM master ports width = 256

• Read/write FIFO depth = 128

• Frame dropping = On

• Frame repeating = On

1,472

19

0

Test Pattern

Generator II

• Color space = RGB

• Run-time control of image size = On

135

0

0

UG-VIPSUITE

2015.05.04

In-System Performance and Resource Guidance

1-9

Video and Image Processing Suite Overview

Altera Corporation