Scaler ii control registers, Scaler ii control registers -14 – Altera Video and Image Processing Suite User Manual

Page 235

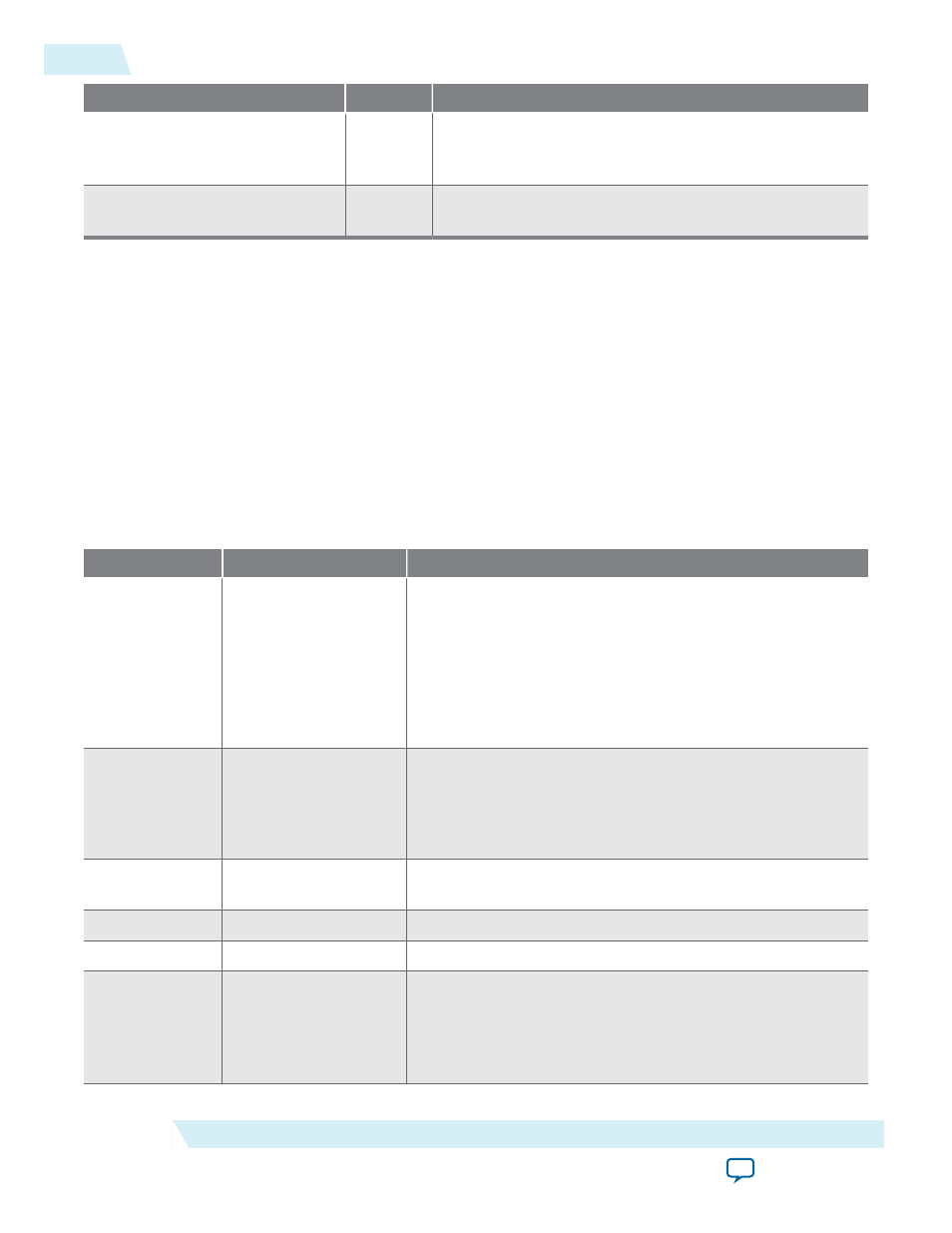

Signal

Direction

Description

control_write

Input

control

slave port Avalon-MM

write

signal. When you

assert this signal, the

control

port accepts new data from

the

writedata

bus.

control_writedata

Input

control

slave port Avalon-MM

writedata

bus. The IP

core uses these input lines for write transfers.

Scaler II Control Registers

The control data is read once at the start of each frame and is buffered inside the IP core, so the registers

can be safely updated during the processing of a frame.

Table 17-5: Scaler II Control Register Map

The coefficient bank that is being read by the IP core must not be written to unless the core is in a stopped state.

To change the contents of the coefficient bank while the IP core is in a running state, you must use multiple

coefficient banks to allow an inactive bank to be changed without affecting the frame currently being processed.

The Scaler II IP core allows for dynamic bus sizing on the slave interface. The slave interface includes a 4-bit byte

enable signal, and the width of the data on the slave interface is 32 bits.

Note: The N

taps

is the number of horizontal or vertical filter taps, whichever is larger.

Address

Register

Description

0

Control

• Bit 0 of this register is the

Go

bit, all other bits are unused.

Setting this bit to 0 causes the IP core to stop the next time

control information is read.

• Bit 1 enables the edge adaptive coefficient selection—set to

1 to enable this feature.

• Bit 2 enables edge adaptive sharpening—set to 1 to enable

this feature.

1

Status

Bit 0 of this register is the

Status

bit, all other bits are unused.

• It is set to 0 if the IP core has not been started.

• It is set to 1 while the IP core is processing data and cannot

be stopped.

2

Interrupt

This bit is not used because the IP core does not generate any

interrupts.

3

Output Width

The width of the output frames in pixels.

4

Output Height

The height of the output frames in pixels.

5

Edge Threshold

Specifies the minimum difference between neighboring pixels

beyond which the edge-adaptive algorithm switches to using

the edge coefficient set. To get the threshold used internally,

this value is multiplied by the number of color planes per

pixel.

17-14

Scaler II Control Registers

UG-VIPSUITE

2015.05.04

Altera Corporation

Scaler II IP Core