Frame buffer control registers, Frame buffer control registers -13 – Altera Video and Image Processing Suite User Manual

Page 210

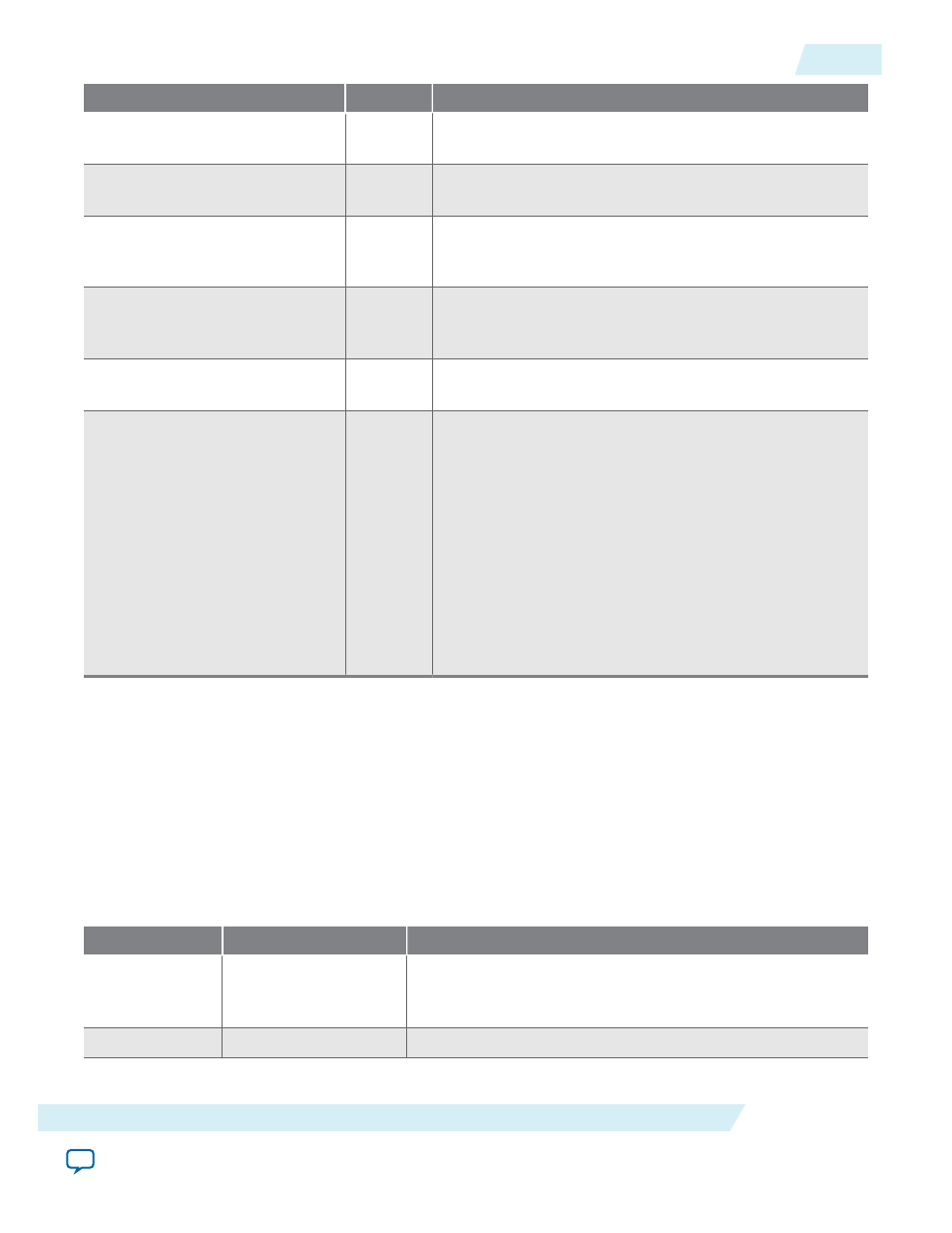

Signal

Direction

Description

mem_master_wr_address

Output

mem_master_wr

port Avalon-MM

address

bus. This bus

specifies a byte address in the Avalon-MM address space.

mem_master_wr_burstcount

Output

mem_master_wr

port Avalon-MM

burstcount

signal.

This signal specifies the number of transfers in each burst.

mem_master_wr_waitrequest

Input

mem_master_wr

port Avalon-MM

waitrequest

signal.

The system interconnect fabric asserts this signal to cause

the master port to wait.

mem_master_wr_write

Output

write_master

port Avalon-MM

write

signal. The IP core

asserts this signal to indicate write requests from the

master to the system interconnect fabric.

mem_master_wr_writedata

Output

mem_master_wr

port Avalon-MM

writedata

bus. These

output lines carry data for write transfers.

mem_master_wr_byteenable

Output

mem_master_wr

slave port Avalon-MM

byteenable

bus.

This bus enables specific byte lane or lanes during

transfers.

Each bit in

byteenable

corresponds to a byte in

writedata

and

readdata

.

• During writes,

byteenable

specifies which bytes are

being written to; the slave ignores other bytes.

• During reads,

byteenable

indicates which bytes the

master is reading. Slaves that simply return

readdata

with no side effects are free to ignore

byteenable

during reads.

Frame Buffer Control Registers

A run-time control can be attached to either the writer component or the reader component of the Frame

Buffer IP cores but not to both. The width of each register is 16 bits.

Table 14-8: Frame Buffer Control Register Map for the Writer

The table below describes the control register map for the writer component.

Note: Addresses 4, 5, and 6 are optional and only visible on the control interface when you turn on Support lock

frame rate conversion in the parameter editor.

Address

Register

Description

0

Control

Bit 0 of this register is the

Go

bit, all other bits are unused.

Setting this bit to 0 causes the IP core to stop the next time

control information is read.

1

Status

Bit 0 of this register is the

Status

bit, all other bits are unused.

UG-VIPSUITE

2015.05.04

Frame Buffer Control Registers

14-13

Frame Buffer IP Cores

Altera Corporation