Altera Video and Image Processing Suite User Manual

Page 183

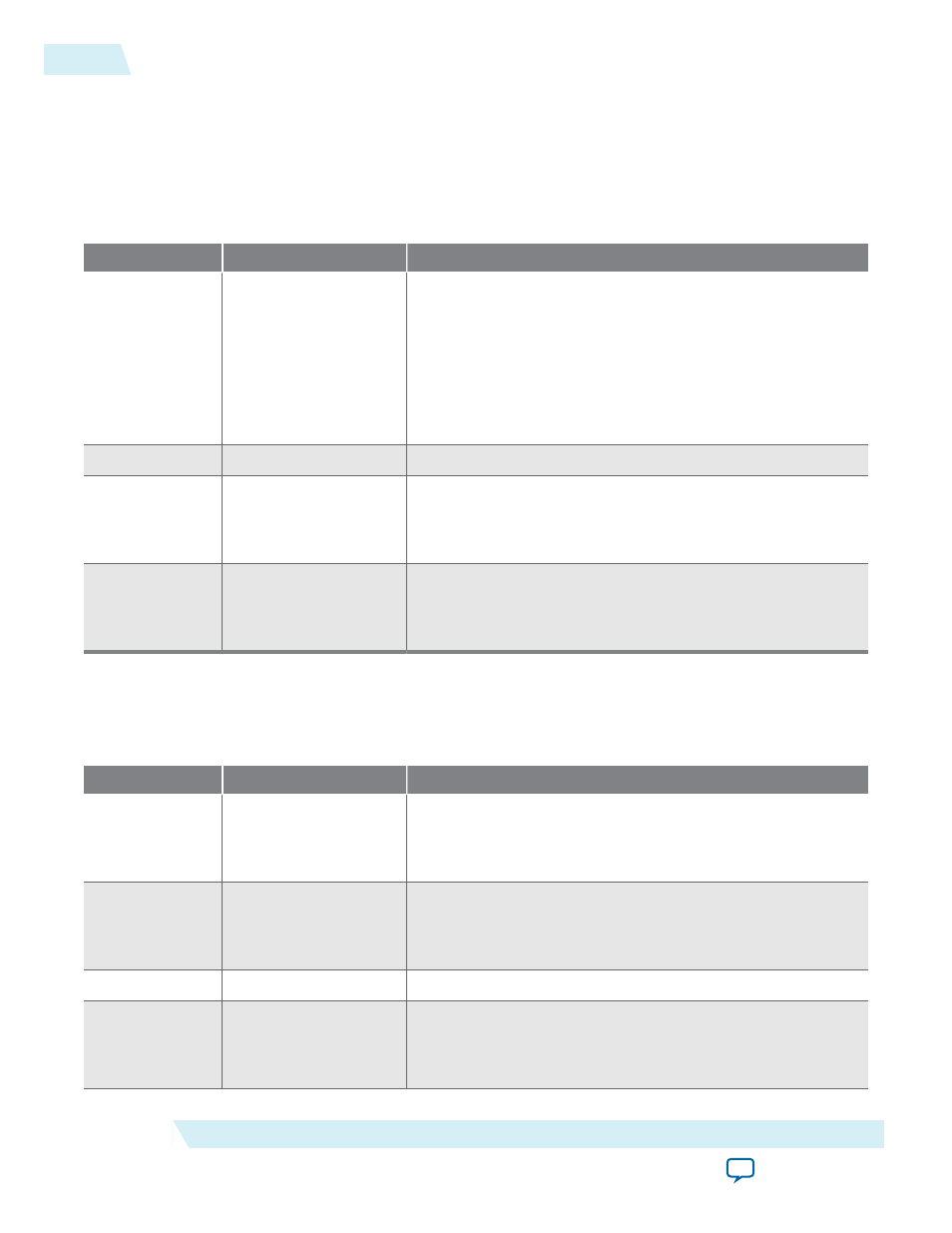

Table 12-9: Deinterlacer Control Register Map for Synchronizing the Input and Output Frame Rates

The table below describes the control register map that synchronizes the input and output frame rates. The

control data is read and registered when receiving the image data header that signals new frame. It can be safely

updated during the processing of a frame.

Note: The behavior of the rate conversion algorithm is not directly affected by a particular choice of input and

output rates but only by their ratio. 23.976—29.970 is equivalent to 24—30.

Address

Register

Description

0

Control

Bit 0 of this register is the

Go

bit, all other bits are unused.

• Setting this bit to 0 causes the Deinterlacer IP core to stop

before control information is read and before receiving

and buffering the next frame.

• While stopped, the Deinterlacer IP core may freeze the

output and repeat a static frame if triple-buffering is

enabled.

1

Status

Bit 0 of this register is the

Status

bit, all other bits are unused.

2

Input frame rate

Write-only register.

An 8-bit integer value for the input frame rate. This register

cannot be read.

3

Output frame rate

Write-only register.

An 8-bit integer value for the output frame rate. This register

cannot be read.

Table 12-10: Deinterlacer II Control Register Map for Run-Time Control of the Motion-Adaptive Algorithm

The table below describes the control register map that controls the motion-adaptive algorithm at run time. The

control data is read once and registered before outputting a frame. It can be safely updated during the processing

of a frame.

Address

Register

Description

0

Control

Bit 0 of this register is the

Go

bit, all other bits are unused.

Setting this bit to 0 causes the Deinterlacer II IP core to stop

after generating the current output frame.

1

Status

Bit 0 of this register is the

Status

bit, all other bits are unused.

When this bit is set to 0, it either gets disabled through the

Go

bit or waits to receive video data.

2

Reserved

This register is reserved for future use.

3

Cadence detect on

• Setting bit 0 of this register to 1 enables cadence detection.

• Setting bit 0 of this register to 0 disables cadence detection.

• Cadence detection is disabled on reset.

12-24

Deinterlacing Control Registers

UG-VIPSUITE

2015.05.04

Altera Corporation

Deinterlacing IP Cores