Interlacer control registers, Interlacer control registers -4 – Altera Video and Image Processing Suite User Manual

Page 221

Signal

Direction

Description

control_av_writedata

Input

control

slave port Avalon-MM

writedata

bus. The IP

core uses these input lines for write transfers.

Interlacer Control Registers

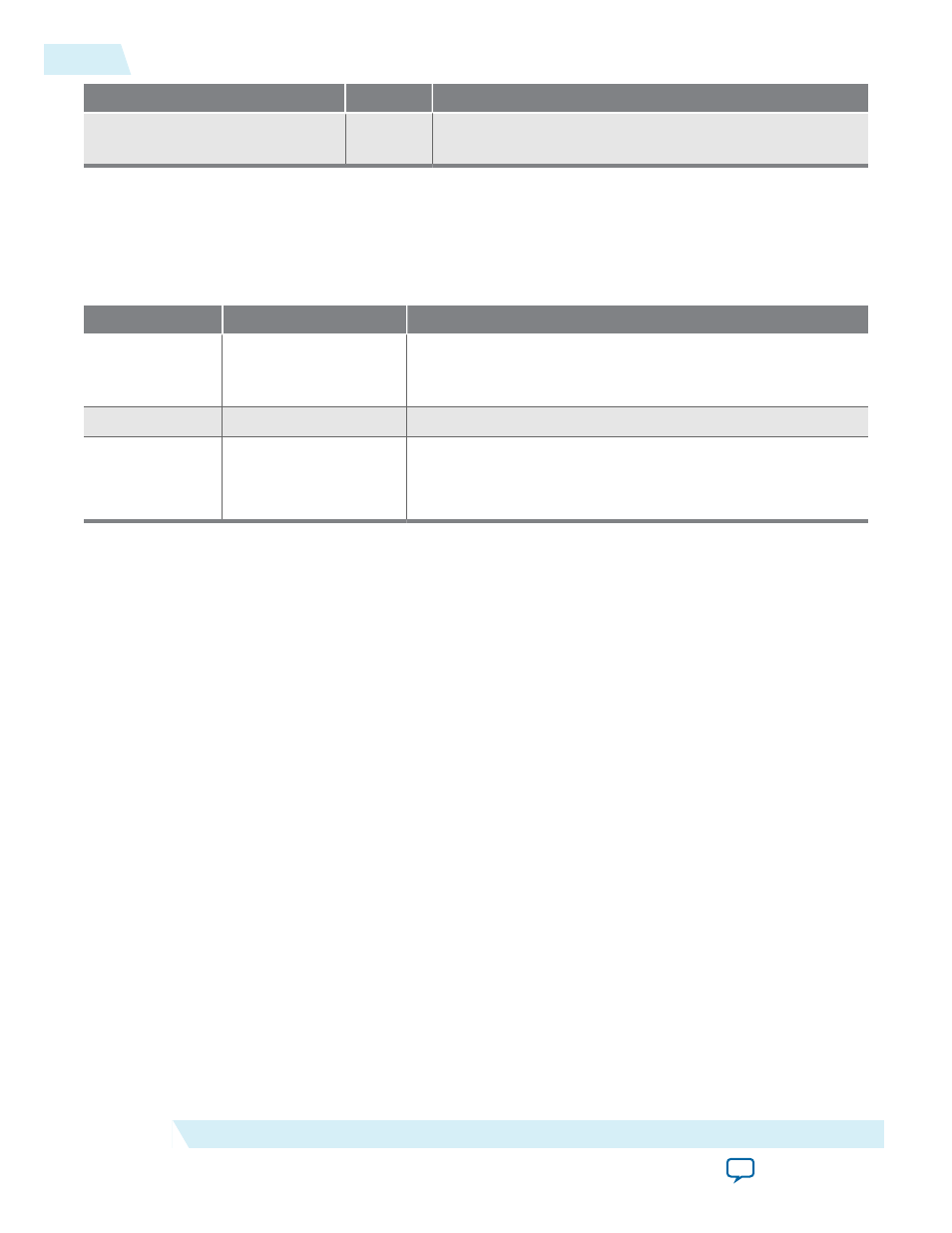

Table 16-4: Interlacer Register Map

The control interface is 8 bits wide but the Interlacer IP core only uses bit 0 of each addressable register.

Address

Register

Description

0

Control

Bit 0 of this register is the

Go

bit. All other bits are unused.

Setting this bit to 1 causes the IP core to pass data through

without modification.

1

Status

Bit 0 of this register is the

Status

bit, all other bits are unused.

2

Progressive pass-

through

Setting bit 0 to 1 disables the Interlacer IP core. When

disabled, progressive inputs are propagated without modifica‐

tion.

16-4

Interlacer Control Registers

UG-VIPSUITE

2015.05.04

Altera Corporation

Interlacer IP Core