2 ) format – Yaskawa MP900 Series Ladder Programming Manual User Manual

Page 231

5.8 DDC Instructions

5.8.7 First-order Lag (LAG)

5-162

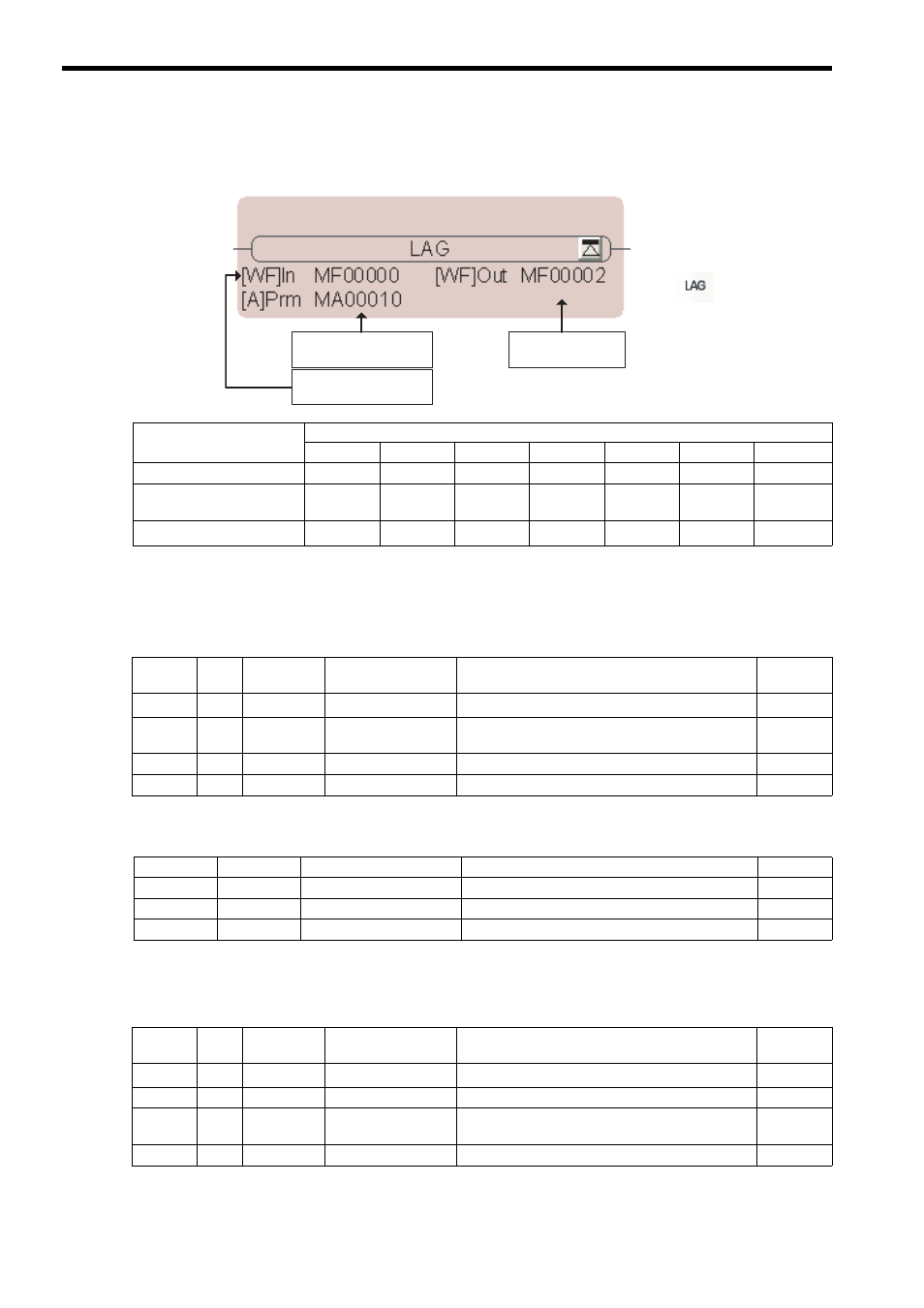

( 2 ) Format

∗ C and # registers cannot be used.

[ a ] Parameter Table Configuration for LAG Instruction with Integers

∗ The relay input and output bits are assigned as given below. (Close = Bit change to 1 (ON), Open = Bit change to 0

(OFF))

[ b ] Parameter Table Configuration for LAG Instruction with Real Numbers

∗ The relay input and output bit assignments are the same as for integers.

Parameter Name

Applicable Data Types

B

W

L

F

A

Index

Constant

Input value (In)

×

{

×

{

×

{

{

First address of parameter

table (Prm)

×

×

×

×

{

*

{

{

Output value (Out)

×

{

*

×

{

*

×

{

×

First address of

parameter table

Output value

Input value

Icon:

Key entry: LAG

Address

Data

Type

Symbol

Name

Specification

I/O

0

W

RLY

Relay I/O

Relay inputs and relay outputs

*

IN/OUT

1

W

T

First-order lag time

constant

First-order lag time constant (ms)

IN

2

W

Y

LAG output

LAG output (output to Out)

OUT

3

W

REM

Remainder

Remainder storage

OUT

Bit

Symbol

Name

Specification

I/O

0

IRST

LAG reset bit

This input is closed to reset the LAG operation.

IN

1 to 7

–

(Reserved.)

Spare input relays

IN

8 to F

–

(Reserved.)

Spare output relays

OUT

Address

Data

Type

Symbol

Name

Specification

I/O

0

W

RLY

Relay I/O

Relay inputs and relay outputs

*

IN/OUT

1

W

–

(Reserved.)

Spare register

–

2

F

T

First-order lag time

constant

First-order lag time constant (s)

IN

4

F

Y

LAG output

LAG output (output to Out)

OUT