Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 100

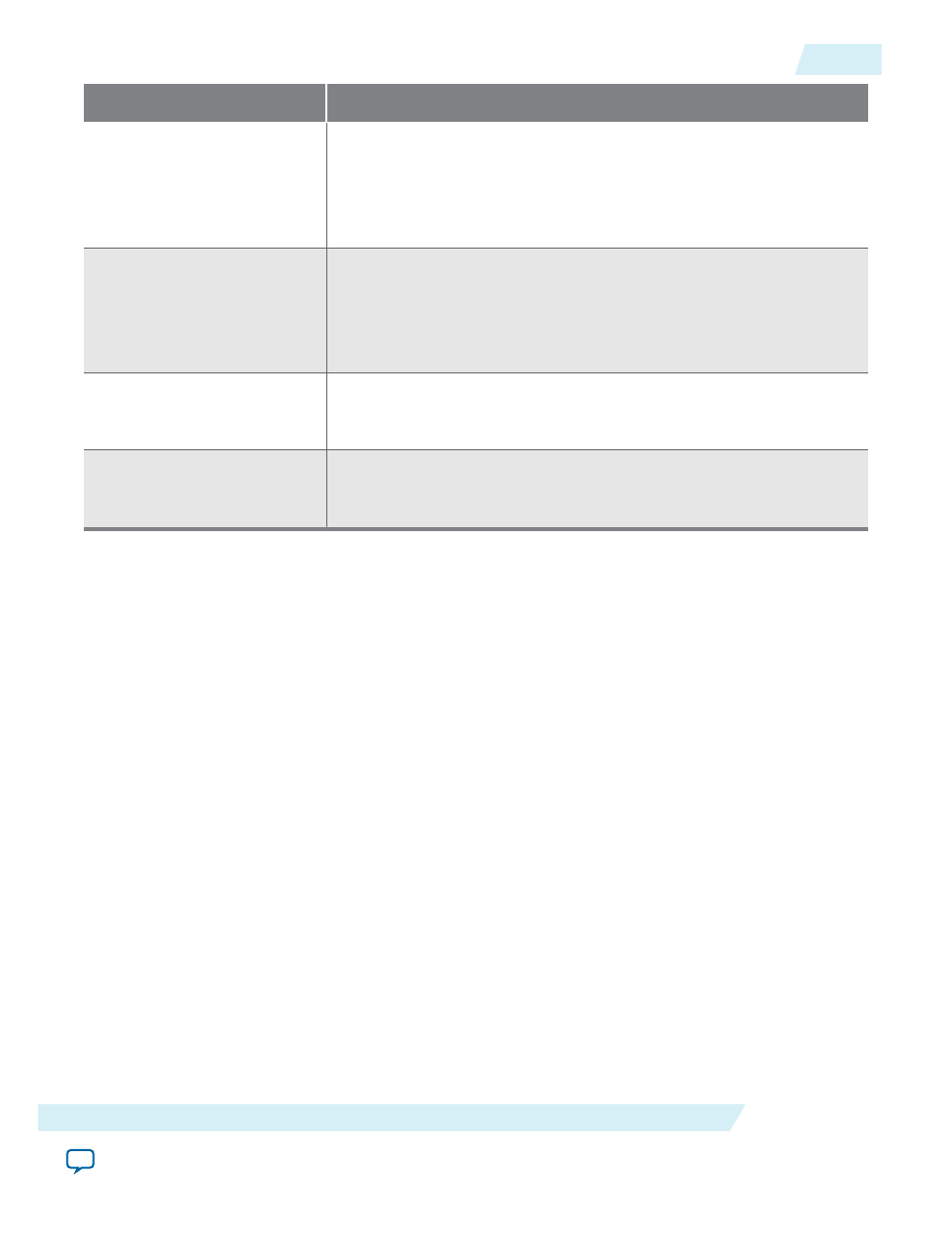

Signal Name

Description

tx_clk_ref

In Sync–E variations (IP core duplex variations with the Sync–E option

enabled), this clock replaces

clk_ref

as the reference clock for the

transceiver TX PLL.

The frequency of this input clock must match the value you specify for

PHY reference frequency in the IP core parameter editor.

rx_clk_ref

In Sync–E variations (IP core duplex variations with the Sync–E option

enabled), this clock replaces

clk_ref

as the reference clock for the

transceiver CDR PLL.

The frequency of this input clock must match the value you specify for

PHY reference frequency in the IP core parameter editor.

clk_txmac

The input TX clock for the IP core with or without adapters is

clk_txmac

.

The recommended TX MAC clock frequency is 190.90 MHz for

24.24 Gbps variations, and 315 MHz for all other IP core variations.

clk_rxmac

The input RX clock for the IP core with or without adapters is

clk_rxmac

.

The recommended TX MAC clock frequency is 190.90 MHz for

24.24 Gbps variations, and 315 MHz for all other IP core variations.

UG-01088

2014.12.15

Clocks

3-53

Functional Description

Altera Corporation