100gbe ip core tx data bus interfaces, 100gbe ip core user interface data bus, 100gbe ip core tx data bus interfaces -6 – Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 53

Related Information

MAC Feature Configuration Registers

on page 3-105

Includes information about the

IPG_DEL_PERIOD

and

IPG_DEL_ENABLE

registers.

40-100GbE IP Core TX Data Bus Interfaces

This section describes the TX data bus at the user interface and includes the following topics:

40-100GbE IP Core User Interface Data Bus

40-100GbE IP Core TX Data Bus with Adapters (Avalon-ST Interface)

on page 3-6

40-100GbE IP Core TX Data Bus Without Adapters (Custom Streaming Interface)

Bus Quantization Effects With Adapters

User Interface to Ethernet Transmission

40-100GbE IP Core User Interface Data Bus

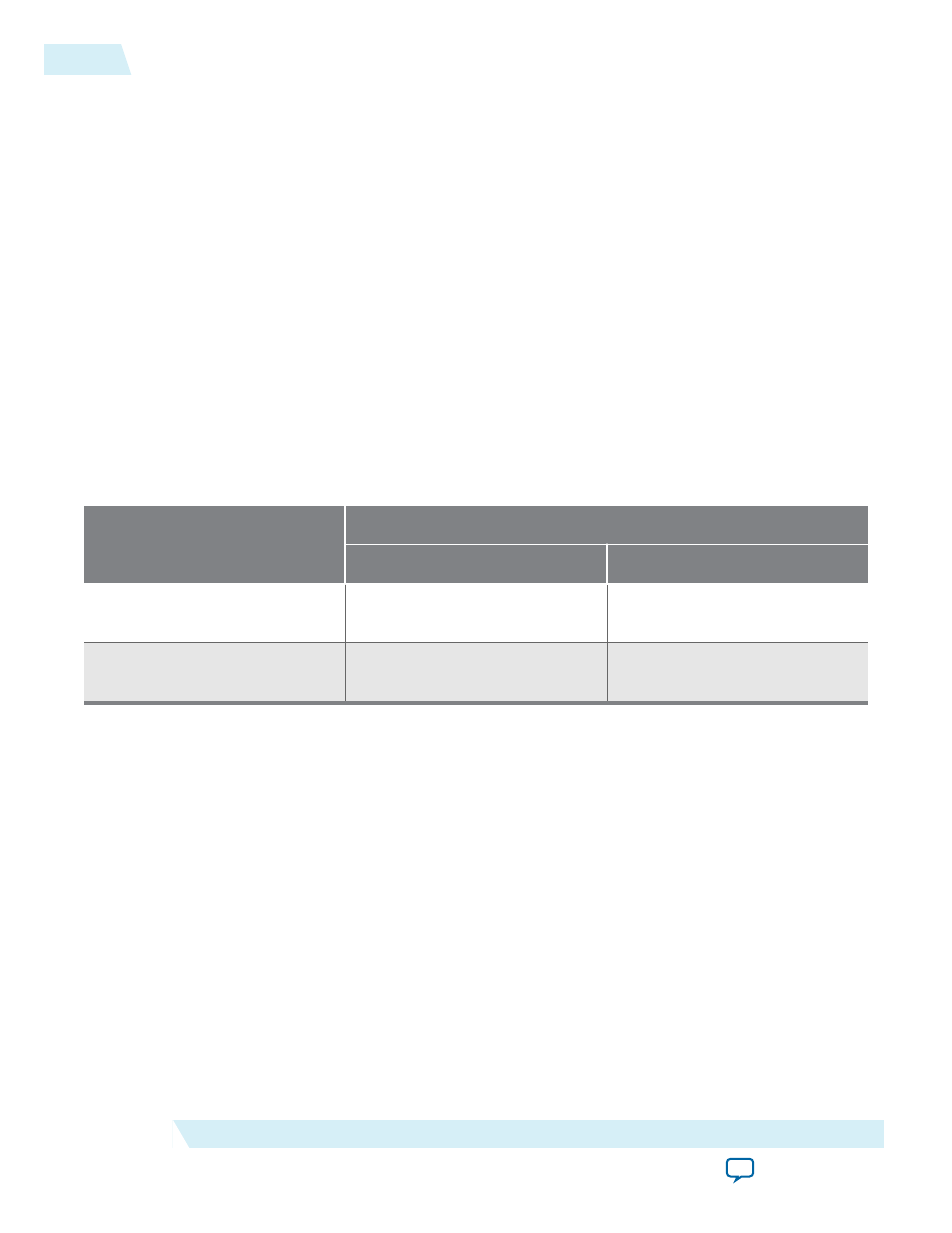

Table 3-1: User Interface Width Depends on IP Core Variation

The 40-100GbE IP core provides two different client interfaces: the Avalon-ST interface and a custom interface.

The Avalon-ST interface requires adapters and the custom streaming interface does not require adapters.

Client Interface

Data Bus Width (Bits)

40GbE IP Core

100GbE IP Core

Custom streaming interface (no

adapters)

128

320

Avalon-ST interface (with

adapters)

256

512

40-100GbE IP Core TX Data Bus with Adapters (Avalon-ST Interface)

The 40-100GbE IP core TX datapath with adapters employs the Avalon-ST protocol. The Avalon-ST

protocol is a synchronous point-to-point, unidirectional interface that connects the producer of a data

stream (source) to a consumer of data (sink). The key properties of this interface include:

• Start of packet (SOP) and end of packet (EOP) signals delimit frame transfers.

• A valid signal qualifies signals from source to sink.

• The sink applies backpressure to the source by using the ready signal. The source typically responds to

the deassertion of the ready signal from the sink by driving the same data until the sink can accept it.

The

readyLatency

defines the relationship between assertion and deassertion of the ready signal, and

cycles which are considered to be

ready

for data transfer.The

readyLatency

on the TX client interface

is zero cycles.

Altera provides an Avalon-ST interface with adapters for both the 40GbE and 100GbE IP cores. The

Avalon-ST interface requires that the start of packet (SOP) always be in the MSB, simplifying the interpre‐

tation and processing of incoming data. The TX adapter for the 100GbE IP core increases the client

interface Avalon-ST bus width from 5 words (320 bits) to 8 words (512 bits). The TX adapter for the

40GbE IP core increases the client interface Avalon-ST bus width from 2 words (128 bits) to 4 words (256

3-6

40-100GbE IP Core TX Data Bus Interfaces

UG-01088

2014.12.15

Altera Corporation

Functional Description