Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 145

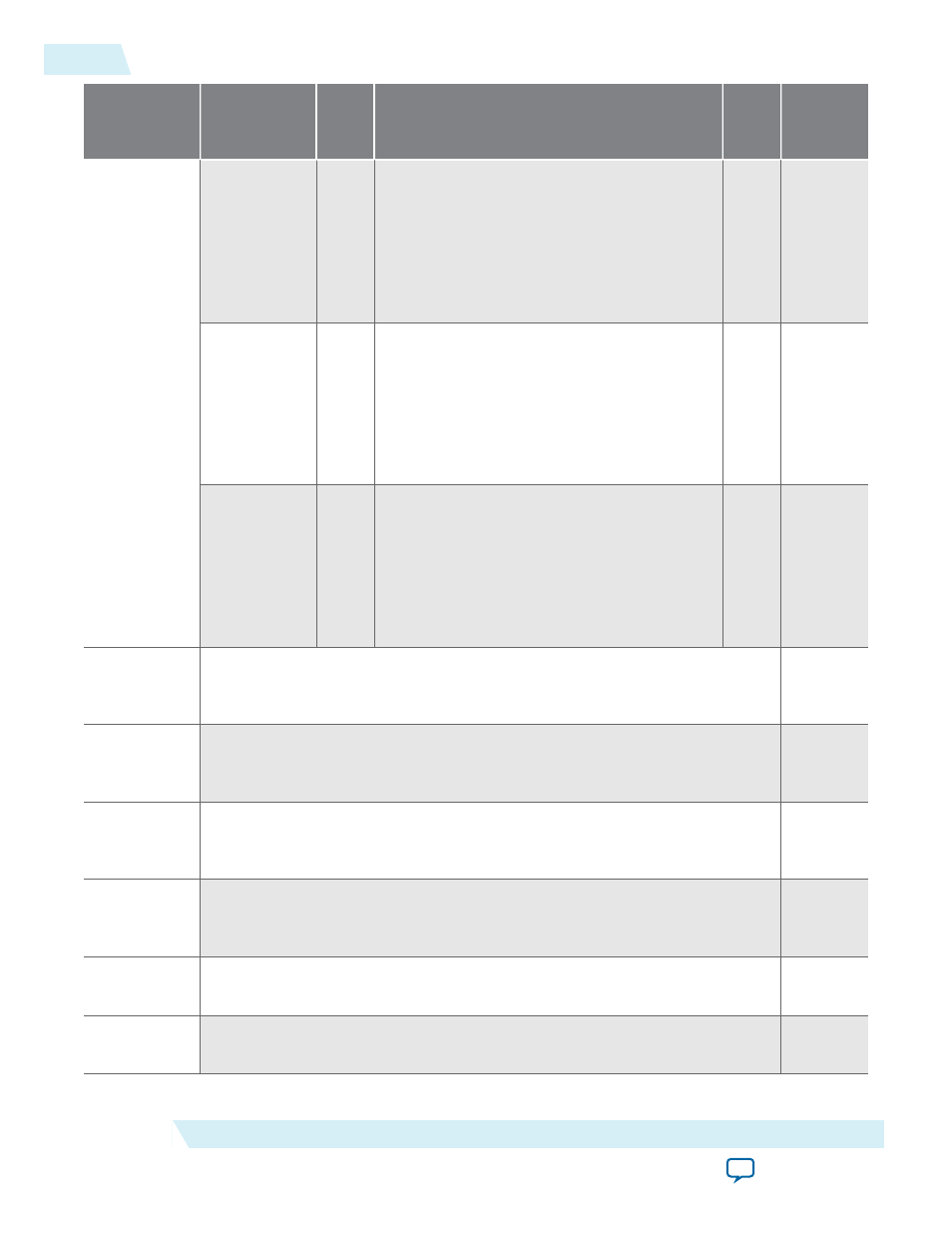

Address

Name

Bit

Description

HW

Reset

Value

Access

0xD2

[15:8] Register bits 0xD2[7:0] refer to Lane 0. These bits

are the equivalent of 0xD2[7:0] for Lane 1. (Refer

10GBASE-KR PHY Register Definitions

For

Link Training Frame lock Error, Lane

1

, if the tap settings specified by the fields of

0xE2 are the same as the initial parameter value,

the frame lock error was unrecoverable.

RO

[23:16

]

These bits are the equivalent of 0xD2[7:0] for

Lane 2. (Refer to

).

For

Link Training Frame lock Error, Lane

2

, if the tap settings specified by the fields of

0xE6 are the same as the initial parameter value,

the frame lock error was unrecoverable.

RO

[31:24

]

These bits are the equivalent of 0xD2[7:0] for

Lane 3. (Refer to

).

For

Link Training Frame lock Error, Lane

3

, if the tap settings specified by the fields of

0xEA are the same as the initial parameter value,

the frame lock error was unrecoverable.

RO

0xE0

Register 0xD3 refers to Lane 0. This register, register 0xE0, is the equivalent of

register 0xD3 for Lane 1 link training. (Refer to

RW

0xE1

Register 0xD4 refers to Lane 0. This register, register 0xE1, is the equivalent of

register 0xD4 for Lane 1 link training. (Refer to

RW

0xE2

Register 0xD5 refers to Lane 0. This register, register 0xE2, is the equivalent of

register 0xD5 for Lane 1 link training. (Refer to

RO

0xE3

Register 0xD6 refers to Lane 0. This register, register 0xE3, is the equivalent of

register 0xD6 for Lane 1 link training. (Refer to

RW

0xE4

This register is the equivalent of register 0xD3 for Lane 2 link training. (Refer to

10GBASE-KR PHY Register Definitions

).

RW

0xE5

This register is the equivalent of register 0xD4 for Lane 2 link training. (Refer to

10GBASE-KR PHY Register Definitions

).

R / RW

3-98

40GBASE-KR4 Registers

UG-01088

2014.12.15

Altera Corporation

Functional Description