Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 76

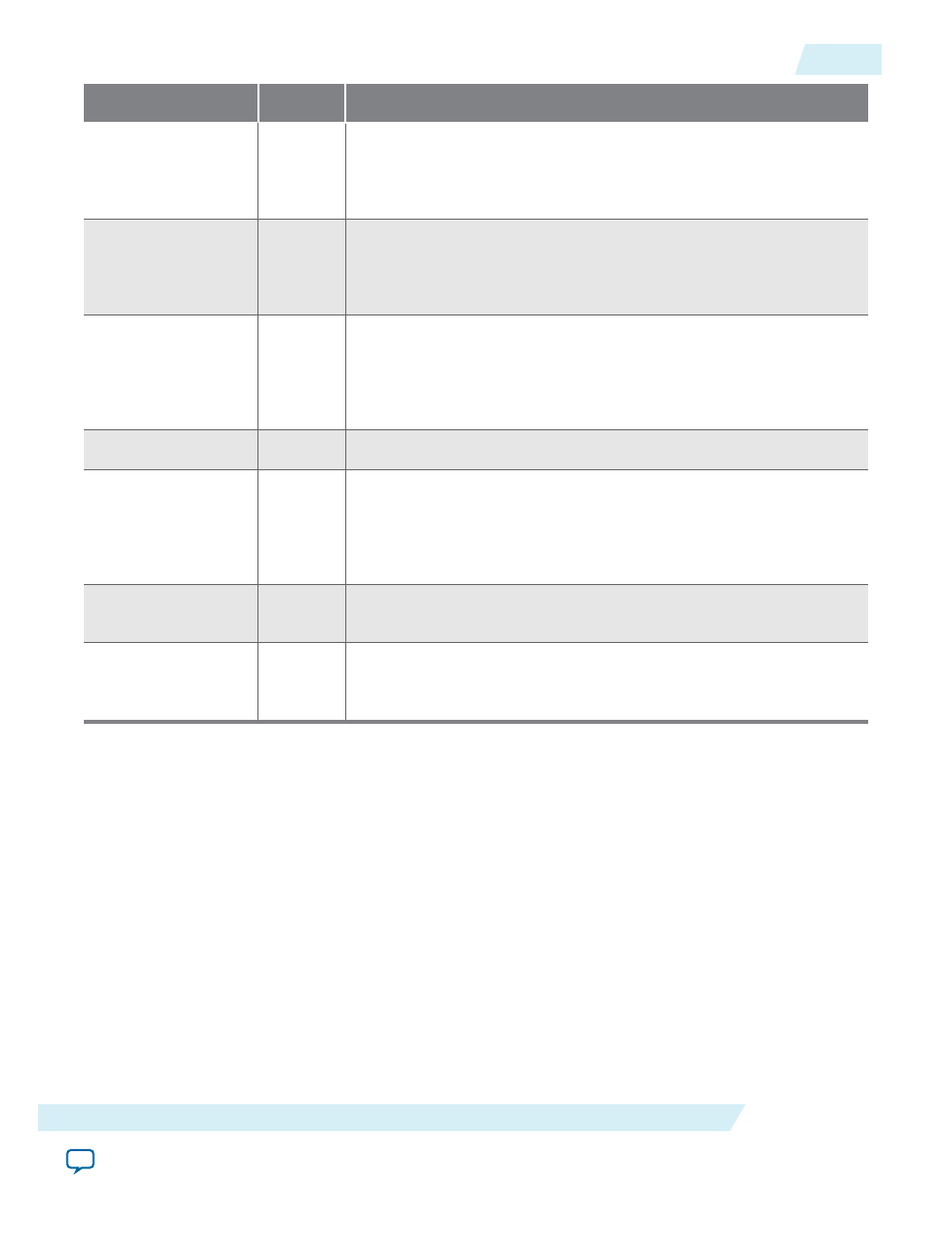

Signal Name

Direction

Description

dout_runt_last_

data[<w>-1:0]

Output

Indicates that the last_data (the final data byte of the frame) is the final

data byte of a runt frame (< 64 bytes). If a frame is eight bytes or

smaller, it is considered a decoding error and not a runt frame, and the

IP core does not flag it with this signal.

dout_payload[<w>

-1:0]

Output

Word contains packet data (including destination and source

addresses) as opposed to only containing Idle bytes. CRC and padding

bits are considered data for this signal. When preamble pass-through is

turned on, the preamble is also considered data for this signal.

dout_fcs_error

Output

The current or most recent last_data byte is part of a frame with an

incorrect FCS (CRC-32) value. By default, the IP core asserts

dout_

fcs_error

in the same cycle as the

dout_last_data

signal. However,

in RX automatic pad removal mode, the

dout_fcs_error

signal might

lag the

dout_last_data

signal for the frame.

dout_fcs_valid

Output

The FCS error bit is valid.

dout_dst_addr_

match[<w>-1:0]

Output

The first data word in a frame that matches the destination address in

the

DST_AD0_LO

and

DST_AD0_HI

registers. However, if bit 30 of the

MADDR_CTRL

register has the value of 0, the address is always considered

to match. Otherwise, if bit 0 of the

MADDR_CTRL

register has the value of

0, the address is always considered to not match.

dout_valid

Output

The

dout_d

bus contents are valid. This signal is occasionally

deasserted due to clock crossing.

clk_rxmac

Input

RX MAC clock. The minimum clock frequency is 315 MHz. The

clk_

rxmac

clock and the

clk_txmac

clock (which clocks the TX datapath)

are not related and their rates do not have to match.

The data bytes use 100 Gigabit Media Independent Interface (CGMII-like) encoding. For packet payload

bytes, the

dout_c

bit is set to 0 and the

dout_d

byte is the packet data. You can use this information to

transmit out-of-spec data such as customized preambles when implementing non-standard variants of the

IEEE 802.3ba-2010 100G Ethernet Standard. If the additional customized data is not required, simply

ignore all words which are marked with

dout_payload

= 0 and discard the

dout_c

bus.

In RX preamble pass-through mode,

dout_c

has the value of 1 while the start byte of the preamble is

presented on the RX interface, and

dout_c

has the value of 0 while the remainder of the preamble

sequence (six-byte preamble plus SFD byte) is presented on the RX interface. While the preamble

sequence is presented on the RX interface,

dout_payload

has the value of 1.

Related Information

•

RX Automatic Pad Removal Control

Information about the automatic pad removal mode and its effect on the

dout_fcs_error

signal.

•

Additional information about the

MADDR_CTRL

,

DST_AD0_LO

, and

DST_AD0_HI

address registers and

how various register settings interact to affect the value of the

dout_dst_addr_match

signal.

UG-01088

2014.12.15

40-100GbE IP Core RX Data Bus Without Adapters (Custom Streaming Interface)

3-29

Functional Description

Altera Corporation