Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 117

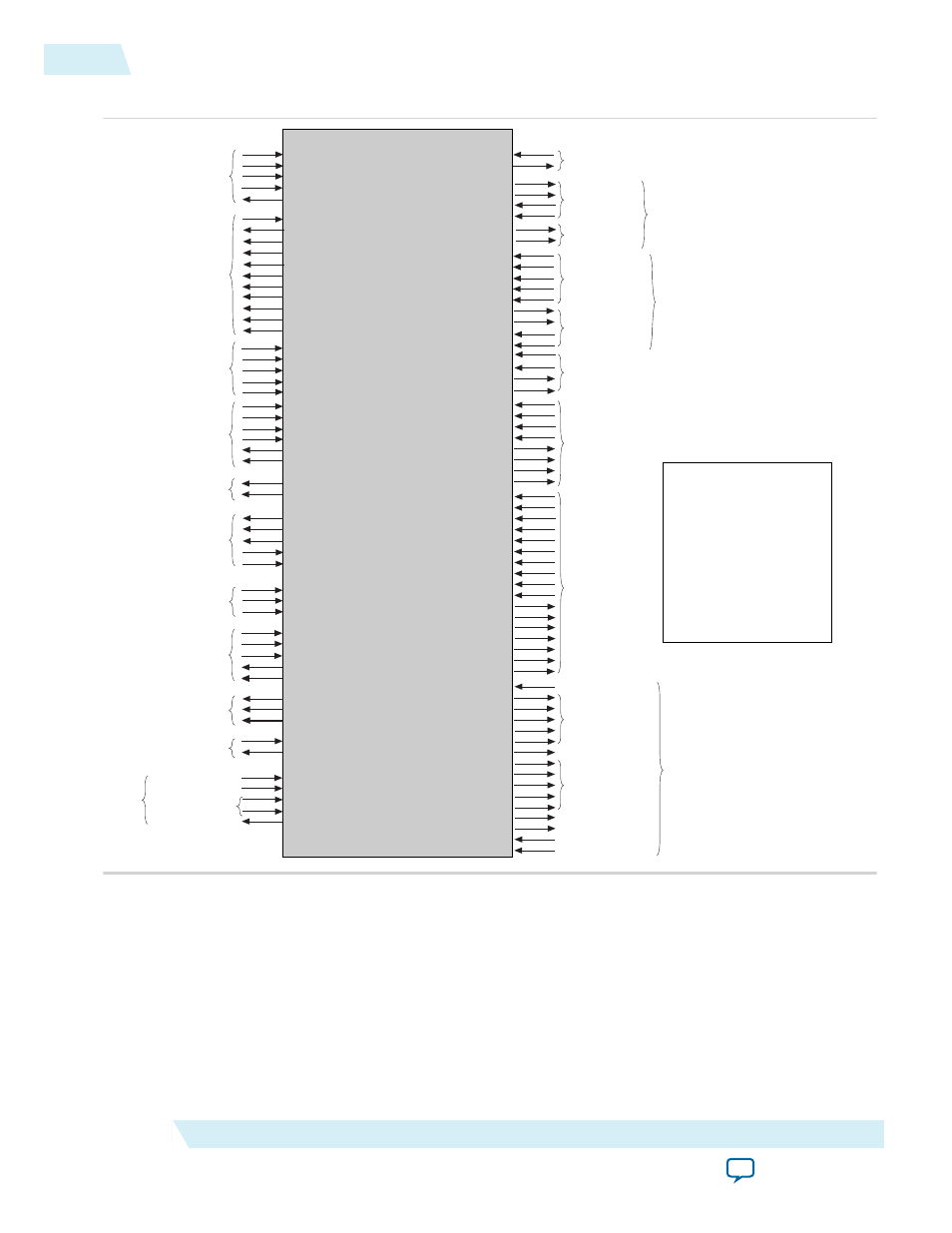

Figure 3-36: Top-Level Signals of the 40-100GbE IP Core Without Adapters

Ethernet Top-Level Signals without Adapters

rx_serial [<v>-1:0]

tx_serial [<v>-1:0]

TX Custom

Streaming

Interface

RX Custom

Streaming

Interface

MAC and PHY

Asynchronous

Reset Signals

Avalon-MM

Control

and Status

Pause Control

and Generation

Legend:

Black = Included in all IP cores.

Blue

= Included in 40-100GbE (alt_e*.v)

and 40-100GbE MAC (alt_e*_mac.v)

Purple

= Included in 40-100GbE (alt_e*.v)

and 40-100GbE PHY (alt_e*_phy.v)

Green

= Included only in 40-100GbE MAC

(alt_e*_mac.v)

Dark Grey

= Included only in 40-100GbE PHY

(alt_e*_phy.v)

TX MAC to PHY

Connections

RX MAC to PHY

Connections

clk_txmac

din [(64 x <w>)-1:0]

din_start [<w>-1:0]

din_end_pos [(8 x < w>)-1:0]

din_ack

clk_rxmac

dout_d [(64 x <w>)-1:0]

dout_c [(8 x <w>)-1:0]

dout_first_data [<w>-1:0]

dout_last_data [(8 x <w>)-1:0]

dout_runt_last_data [<w>-1:0]

dout_payload [<w>-1:0]

dout_fcs_error

dout_fcs_valid

dout_dst_addr_match [<w>-1:0]

dout_valid

mac_rx_arst_ST

mac_tx_arst_ST

pcs_rx_arst_ST

pcs_tx_arst_ST

pma_arst_ST

status_addr [15:0]

status_read

status_write

status_writedata [31:0]

status_readdata [31:0]

status_readdata_valid

pause_insert_tx

pause_insert_time [15:0]

pause_insert_mcast

pause_insert_dst [47:0]

pause_insert_src [47:0]

pause_match_from_rx

pause_time_from_rx [15:0]

pause_match_to_tx

pause_time_to_tx [15:0]

remote_fault_from_rx

local_fault_from_rx

remote_fault_to_tx

local_fault_to_tx

remote_fault_status

local_fault_status

tx_mii_d [(64 x <w>-1):0]

tx_mii_c [(8 x <w>) -1:0]

tx_mii_valid

tx_mii_ready

tx_lanes_stable

rx_mii_d [(64 x <w>-1):0]

rx_mii_c [(8 x <w>-1):0]

rx_mii_valid

Transceiver Serial

Data <v> lanes

@ 10.3125 Gbps or

25.78125 Gbps

Increment Vectors of

Statistics Counters

rx_statistic_counters[22:0]

tx_statistic_counters[21:0]

Pause Status Signaling

(only used internally

when in duplex mode)

clk_status

clk_ref

tx_clk_ref

rx_clk_ref

rx_recovered_clk

lanes_deskewed

lanes_deskewed

Lane to Lane

Deskew

TX MAC to PHY

Connections

RX MAC to PHY

Connections

tx_mii_d [(64 x <w>)-1:0]

tx_mii_c [(8 x <w>) -1:0]

tx_mii_valid

tx_mii_ready

tx_lanes_stable

rx_mii_d [(64 x <w>)-1:0]

rx_mii_c [(8 x <w>)-1:0]

rx_mii_valid

reconfig_to_xcvr[(140 x <v>)-1:0]

reconfig_to_xcvr[(70 x <v>)-1:0]

reconfig_from_xcvr[(92 x <v>)-1:0]

reconfig_from_xcvr[(46 x <v>)-1:0]

reconfig_to_xcvr0[209:0]

reconfig_to_xcvr1[209:0]

reconfig_to_xcvr2[209:0]

reconfig_to_xcvr3[209:0]

reconfig_from_xcvr0[137:0]

reconfig_from_xcvr1[137:0]

reconfig_from_xcvr2[137:0]

reconfig_from_xcvr3[137:0]

External Reconfiguration

Controller for Arria V GZ

and Stratix V Devices

External Reconfiguration

Controller for 100GbE

CAUI-4 Configurations Only

upi_mode_en[3:0]

upi_adj[7:0]

upi_inc[3:0]

upi_dec[3:0]

upi_pre[3:0]

upi_init[3:0]

upi_st_bert[3:0]

upi_train_err[3:0]

KR4 Microprocessor

Interface for

40GBASE-KR4

Microprocessor-Enabled

Configurations Only

upi_lock_err[3:0]

upi_rx_trained[3:0]

upo_cm_done[3:0]

upo_bert_done[3:0]

upo_ber_cnt[47-1:0]

upo_ber_max[3:0]

upo_coef_max[3:0]

upo_enable[3:0]

upo_frame_lock[3:0]

rc_busy[3:0]

lt_start_rc[3:0]

main_rc[23:0]

post_rc[19:0]

pre_rc[15:0]

tap_to_upd[11:0]

seq_start_rc[3:0]

dfe_start_rc[3:0]

Reconfiguration

Interface for

40GBASE-KR4

Reconfiguration-Enabled

Configurations Only

Link Training

Interface for

40GBASE-KR4

Link Training-Enabled

Configurations Only

dfe_mode[7:0]

ctle_start_rc[3:0]

pcs_mode_rc[5:0]

en_lcl_rxeq[3:0]

rxeq_done[3:0]

reco_mif_done

ctle_rc[15:0]

ctle_mode[7:0]

Link Fault

Signaling

(only used internally

when in duplex mode)

(duplex mode only)

(replace clk_ref

in Sync-E variations)

Clocks

(Sync-E variations only)

RX Equalization

Interface for

40GBASE-KR4

RX Equalization-Enabled

Configurations Only

40-100GbE IP core variations that do not include a PHY have the following differences from the

variations that include the PHY:

• The 40-100GbE PHY output signals are not available in the MAC-only variations.

• The MAC-only variations include an interface to connect to a PHY.

3-70

Signals of 40-100GbE MAC‑Only IP Core Variations

UG-01088

2014.12.15

Altera Corporation

Functional Description