Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 106

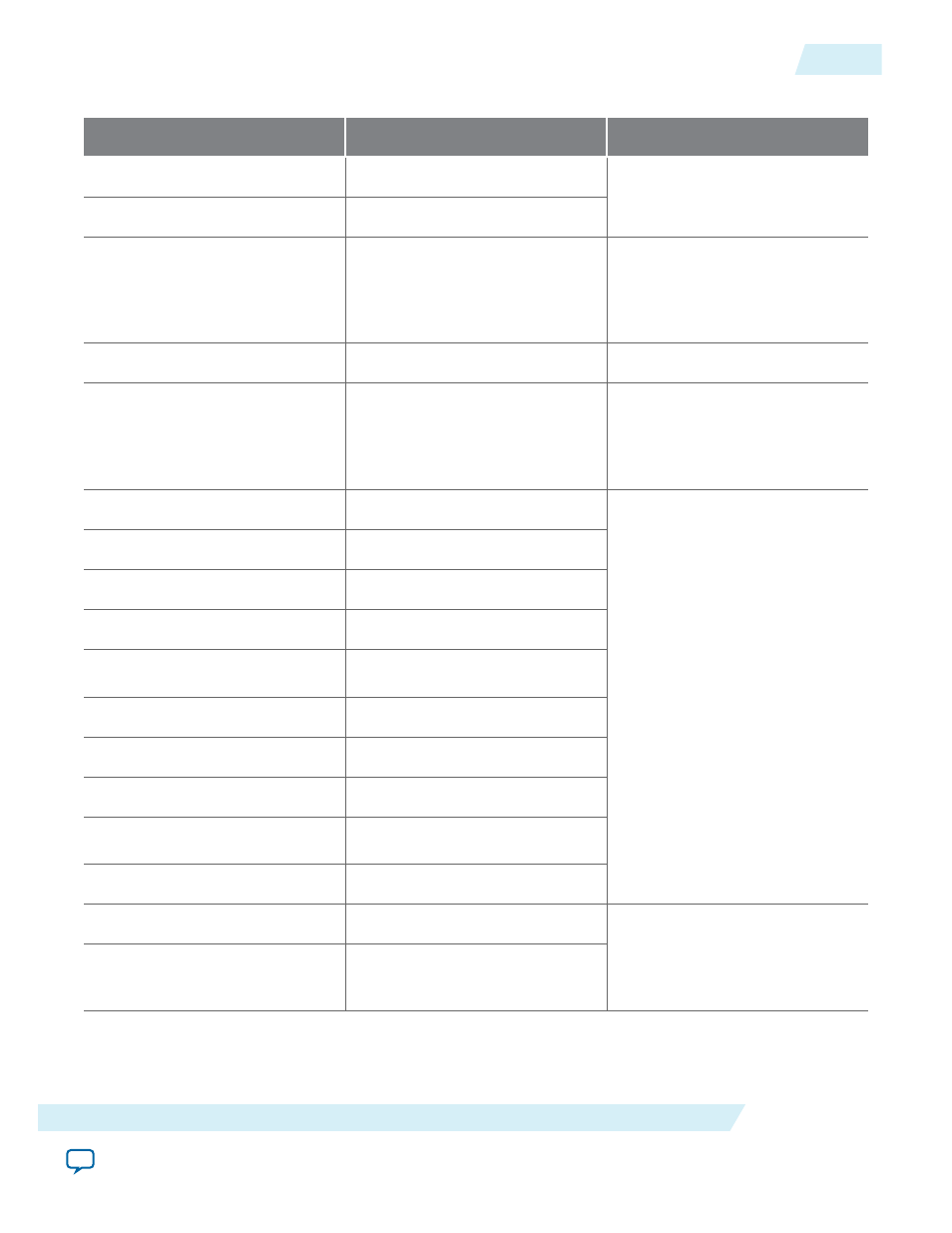

Table 3-19: 40-100GbE MAC and PHY IP Core Without Adapters: Receive Side Signals

Signal Name

Direction

Description

mac_rx_arst_ST

Input

Resets

pcs_rx_arst_ST

Input

rx_serial

[3:0]

(40GbE and

CAUI–4)

rx_serial

[9:0]

(standard

100GbE)

Input

Transceiver PHY serial data

interface

lanes_deskewed

Output

PHY status

clk_rxmac

Input

Clocks

RX client interface without

adapters (custom streaming

interface)

dout_d[<w>*64-1:0]

Output

RX client interface without

adapters (custom streaming

interface)

dout_c[<w>*8-1:0]

Output

dout_first_data[<w>-1:0]

Output

dout_last_data[<w>*8-1:0]

Output

dout_runt_last_data[<w>-

1:0]

Output

dout_payload[<w>-1:0]

Output

dout_fcs_error

Output

dout_fcs_valid

Output

dout_dst_addr_match[<w>-

1:0]

Output

dout_valid

Output

pause_match_from_rx

Output

Pause control and generation

interface

These two signals are not visible

in duplex variations.

pause_time_from_rx[15:0]

Output

UG-01088

2014.12.15

Signals of MAC and PHY Variations Without Adapters

3-59

Functional Description

Altera Corporation