Mac to phy connection interface, Lane to lane deskew interface, Lane to lane deskew interface -43 – Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 90

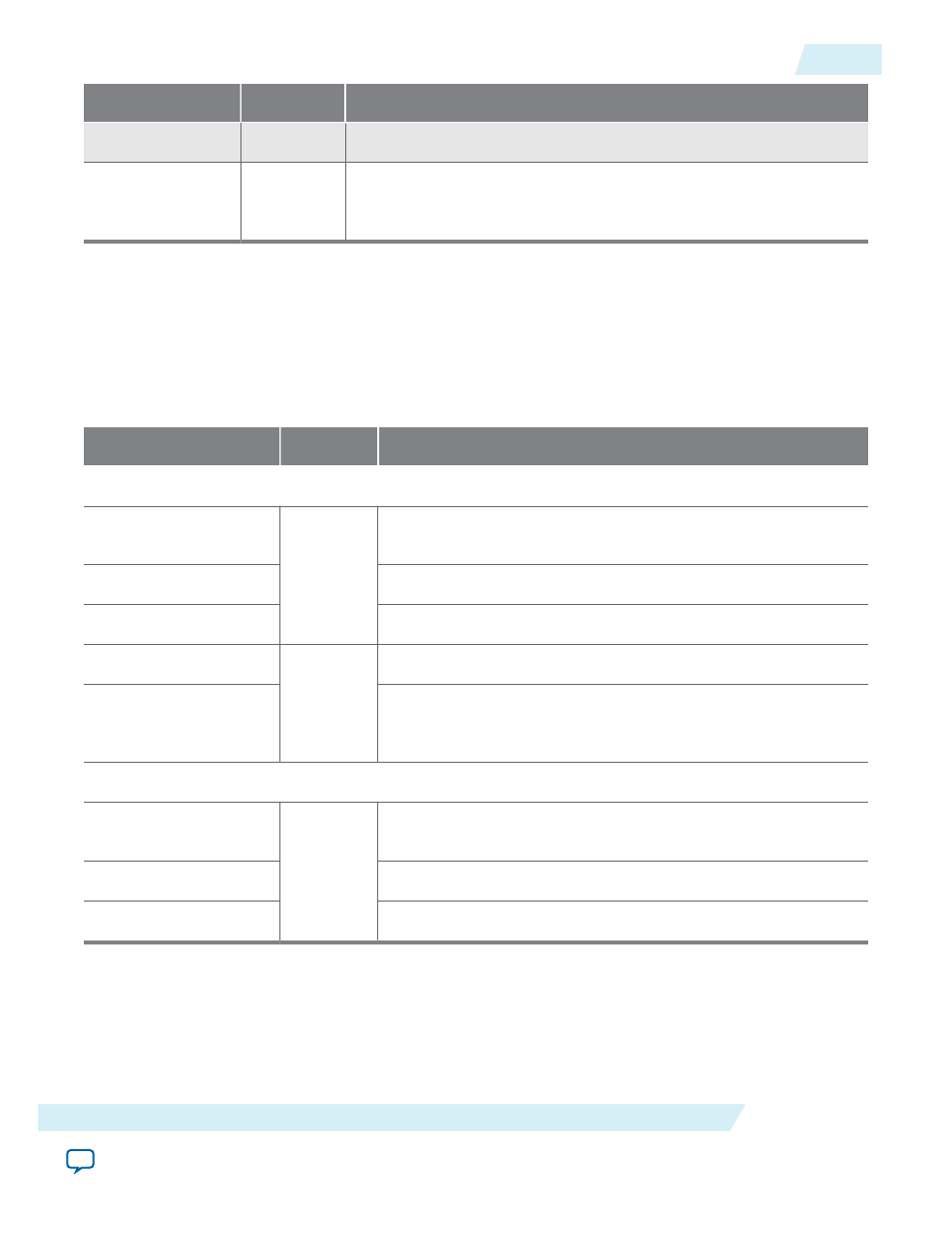

Control

Data

Description

1

fd

End of Frame (fd = frame done).

1

fe

XL/CGMII Error. Typically a bit error which switched a 66-bit block

between data and control, or corrupt control information (fe = frame

error).

MAC to PHY Connection Interface

Table 3-11: MAC to PHY and PHY to MAC TX and RX Signals

The MAC–PHY connection interface is exposed in the 40-100GbE MAC-only and PHY-only IP core variations.

In addition, the

tx_lanes_stable

output signal from the PHY component is available to provide status informa‐

tion to user logic in PHY-only IP core variations and in MAC and PHY IP core variations.

In the table, <w> = 2 for the 40GbE IP core and <w> = 5 for the 100GbE IP core.

Signal Name

Direction

Description

TX Connections (Data from MAC to PHY)

tx_mii_d[<w>*64-

1:0]

Output

from MAC

and input to

PHY

Media independent interface (MII) data TX connection, starting

with the least significant bit (LSB).

tx_mii_c[<w>*8-1:0]

MII control TX connection.

tx_mii_valid

Asserted upon valid TX to MII connection.

tx_mii_ready

Output

from PHY

and input to

MAC

Asserted when TX data bus is ready for MII connection.

tx_lanes_stable

Asserted when TX lanes are stable and deskewed. This signal is

available as an output status signal in MAC and PHY IP core

variations as well as in PHY-only variations.

RX Connections (Data from PHY to MAC)

rx_mii_d[<w>*64-

1:0]

Output

from PHY

and input to

MAC

MII data RX connection, starting with the LSB and least signifi‐

cant word, outputting a 5-word data stream.

rx_mii_c[<w>*8-1:0]

MII control RX connection.

rx_mii_valid

Asserted when RX blocks are valid.

Lane to Lane Deskew Interface

The lane to lane deskew signal is included in the 40-100GbE IP core with and without adapters. When

both MAC and PHY options are selected, the lane to lane deskew input signal acts as an internal signal.

The lane to lane deskew output signal from the PHY component is available to provide status information

to user logic in both PHY-only and MAC and PHY IP core variations.

UG-01088

2014.12.15

MAC to PHY Connection Interface

3-43

Functional Description

Altera Corporation