Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 130

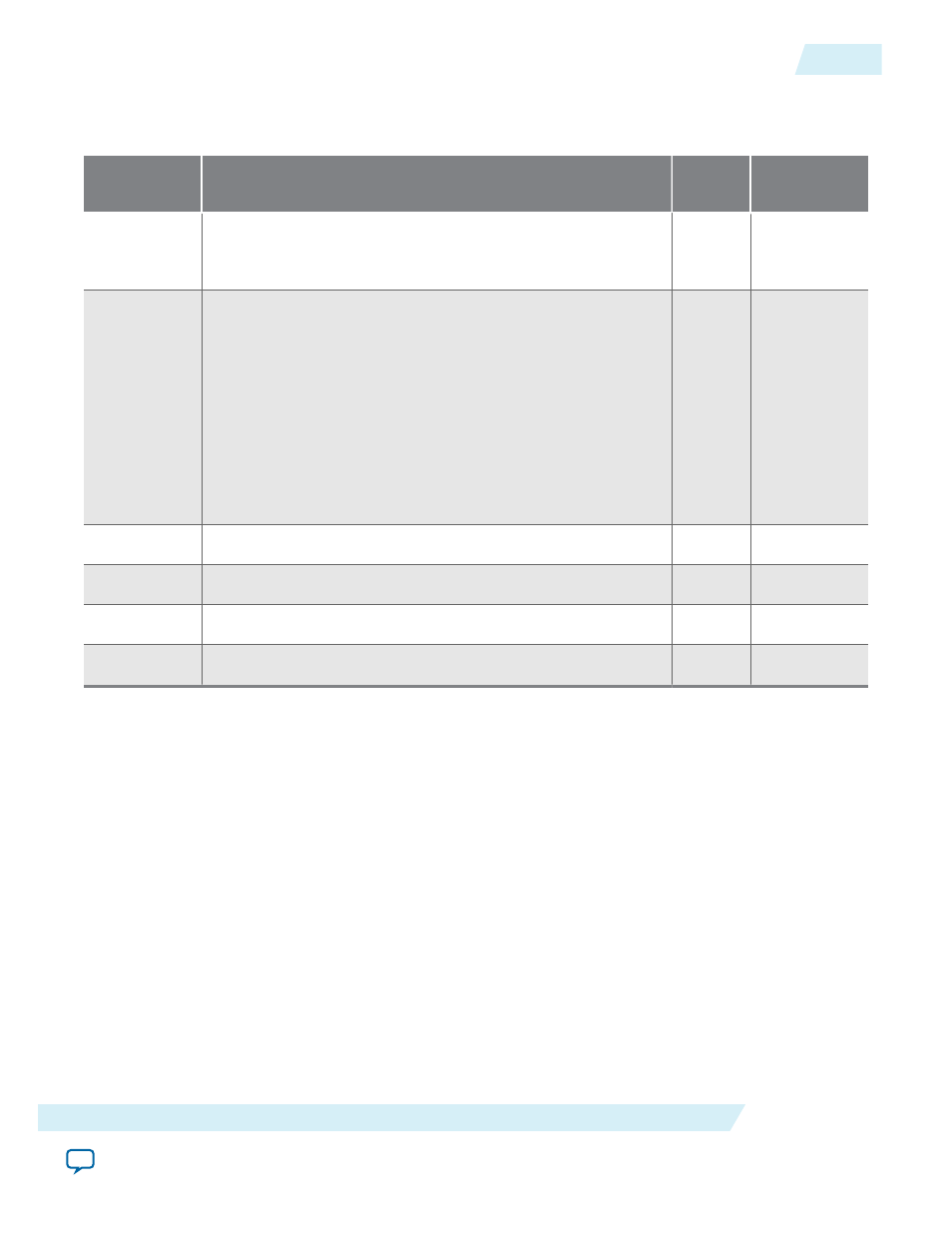

Table 3-27: Stratix IV Transceiver Analog Settings Register GX_CTRL1—Offset 0x007—Bits [28:4]

Describes the fields in bits [28:4] of the analog settings register, GX_CTRL1. The default settings are a good

starting point if you are connecting to a PMD module running at 10.3125 Gbps.

Bits

Description

HW Reset

Value

Access

[28:25]

RX equalization control. The equalizer uses a pass band filter.

Specifying a low value passes low frequencies. Specifying a high

value passes high frequencies.

4’b0011

RW

[24:22]

RX DC gain. Sets the equalization DC gain using one of the

following settings:

• 0: 0 dB

• 1: 3 dB

• 2: 6 dB

• 3: 9 dB

• 4: 12 dB

• 5: 15 dB

• 6: 18 dB

• 7: 21 dB

3’b000

RW

[21:17]

Sets the pre-emphasis for TX tap 0.

5’b10000 RW

[16:12]

Sets the pre-emphasis for TX pre-emphasis tap 1.

5’b00000 RW

[11:7]

Sets the pre-emphasis for TX pre-emphasis tap 2.

5’b10000 RW

[6:4]

TX V

OD

(amplitude).

3’b010

RW

If you encounter signal integrity problems using the default settings in the table, the following procedure

might be helpful:

1. Adjust V

OD

. A value that is too high tends to cause interference with other lanes. You should select the

lowest value that functions correctly.

2. Raise pre-emphasis tap 1 slightly. Raising tap 1 tends to help in the case of long trace length or multiple

connectors causing signal loss.

3. Adjust the equalization control. This control is roughly analogous to a stereo equalizer. It emphasizes

and de-emphasizes portions of the signal by frequency.

4. Repeat these steps, starting at step 1, making minor adjustments to all of the controls while monitoring

the error rate. Note that the controls do interact.

Related Information

•

on page 3-51

For information about required frequencies for the core clocks (

clk_txmac

and

clk_rxmac

) and the

transceiver reference clock (

clk_ref

).

•

For information about Stratix V and Arria V GZ transceiver PHY IP control and status registers.

UG-01088

2014.12.15

Transceiver PHY Control and Status Registers

3-83

Functional Description

Altera Corporation