Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 183

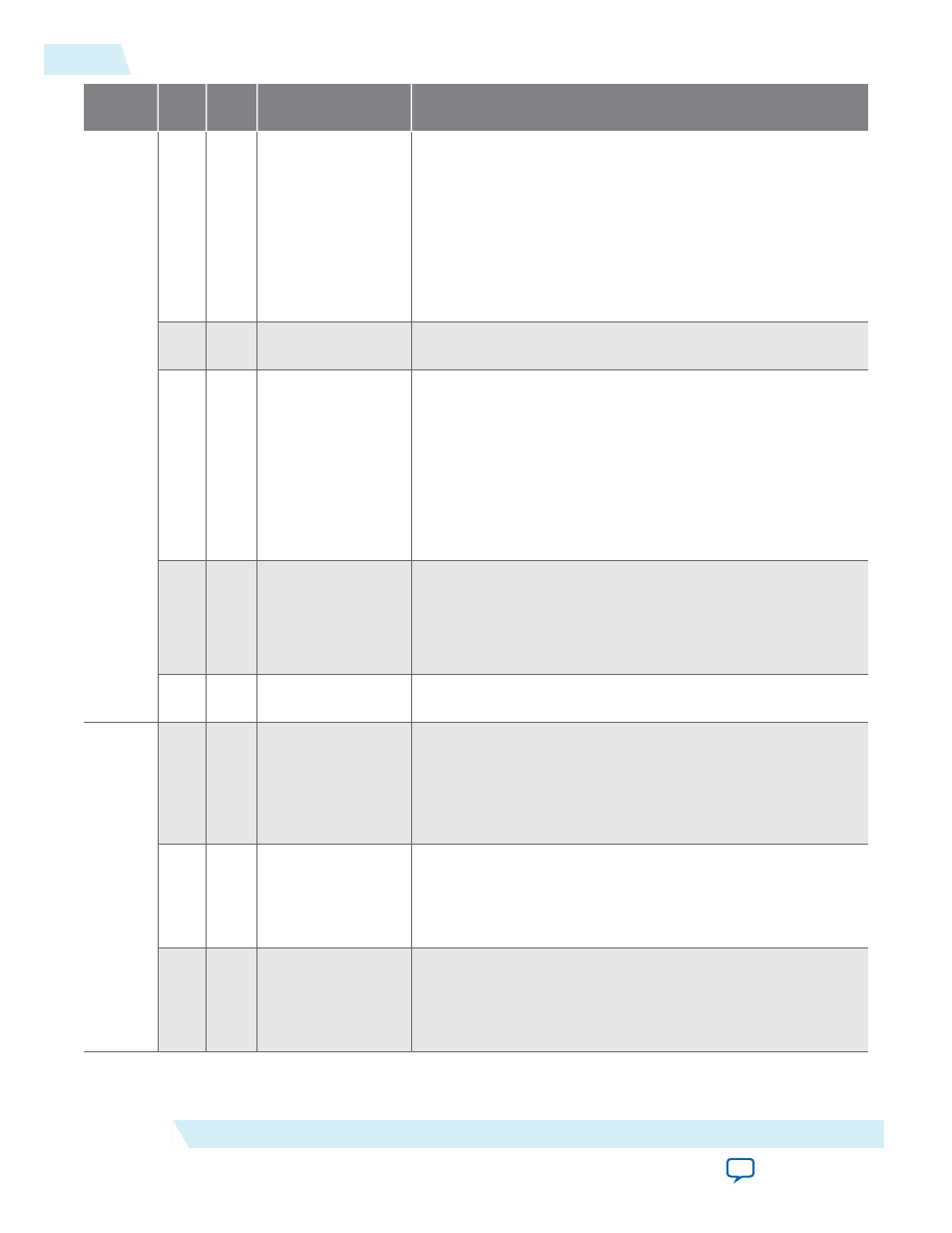

Word

Addr

Bit

R/W

Name

Description

22:20 RW

rx_ctle_mode

RX CTLE mode in the Link Training algorithm. The default

value is 3'b000. The following encodings are defined:

• 3'b000: CTLE tuning in link training is disabled. Retains

user set value of CTLE.

• 3'b001: Reserved.

• 3'b010: Reserved.

• 3'b011: CTLE tuning in link training is enabled.

• 3'b100 to 3'b111: reserved.

23

RW

vod_up

When set to 1, V

OD

is trained to high values. The default is

set to 0 to save power and reduce crosstalk on the link.

26:24 RW

rx_dfe_mode

RX DFE mode in the link training algorithm. The default

value is 3'b000. The following bits are defined:

• 3'b000: DFE adaptation in link training is disabled

• 3'b001: Reserved

• 3'b010: DFE is triggered at the end of link training

• 3'b011: DFE is triggered at the end of V

OD

, Post tap and

Pre-tap training

• 3'b100 to 3'b111: Reserved

28

RW

max_mode

When set to 1, link training operates in maximum TX

equalization mode. Modifies the link training algorithm to

settle on the max pretap and max V

OD

if the BER counter

reaches the maximum for all values. Link training settles on

the

max_post_step

for the posttap value.

31:29 RW

max_post_step

Number of TX posttap steps from the initialization state

when in

max_mode

.

0xD1

0

RW

Restart Link

training

When set to 1, resets the 10GBASE-KR start-up protocol.

When set to 0, continues normal operation. This bit self

clears. For more information, refer to the state variable mr_

restart_training as defined in Clause 72.6.10.3.1 and

10GBASE-KR PMD control register bit (1.150.0) IEEE

802.3ap

-

2007.

4

RW

Updated TX Coef

new

When set to 1, there are new link partner coefficients

available to send. The LT logic starts sending the new values

set in 0xD4 bits[7:0] to the remote device. When set to 0,

continues normal operation. This bit self clears. Must enable

this override in 0xD0 bit16.

8

RW

Updated RX coef

new

When set to 1, new local device coefficients are available. The

LT logic changes the local TX equalizer coefficients as

specified in 0xD4 bits[23:16]. When set to 0, continues

normal operation. This bit self clears. Must enable the

override in 0xD0 bit17.

C-10

10GBASE-KR PHY Register Definitions

UG-01088

2014.12.15

Altera Corporation

10GBASE-KR Registers