Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 60

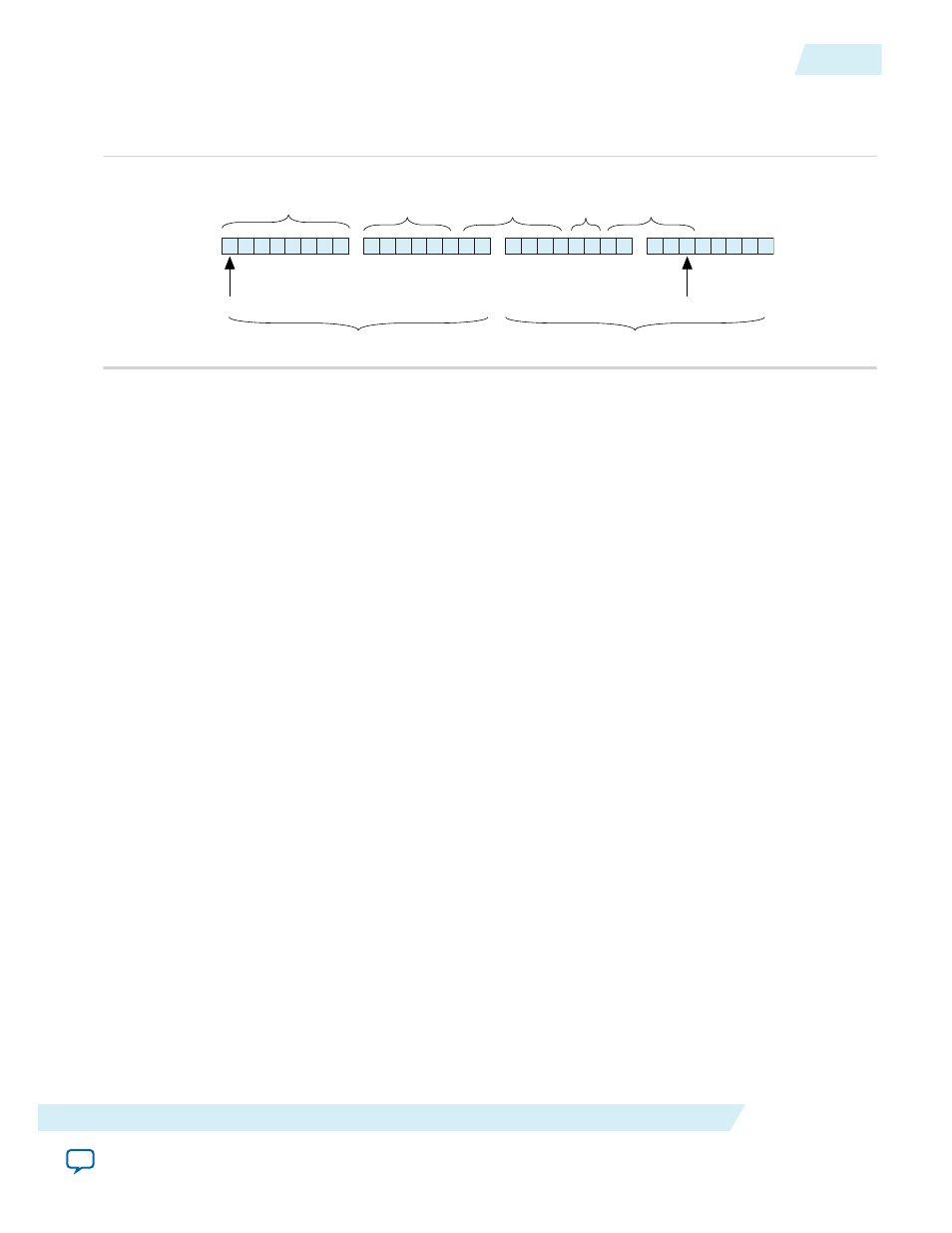

Figure 3-9: Short Packet Example With Preamble

Illustrates the transmission of a short packet when preamble pass-through is turned on. In this example,

the preamble starts in the MSB; however, this need not be the case.

First data

First cycle

Second cycle

Destination

MAC addr

Source

MAC Addr

Preamble,

including Start (ignored)

and SFD

Total

length

Last data

“hello”

Example 3-2: Bus Representation of a Short TX Packet With Preamble

This example shows the Verilog HDL code that represents the simple packet illustrated in the

previous figure. Note that bit

din_end[5]

in the second cycle, corresponding to the “Last data” in

the figure, is asserted.

wire [8*8-1:0] preamble = 64’hXX55_5555_55D5;

wire [6*8-1:0] dst_addr = 48’hffff ffff ffff;

wire [6*8-1:0] src_addr = 48’h0007 edff 1234;

wire [2*8-1:0] len = 16’d64;

\\First cycle:

din = {preamble, dst_addr, src_addr[47:32]};

din_start = 2'b10;

din_end = 16'b00000000_00000000;

\\Second cycle:

din = {src_addr[31:0], len, "hello", 40'h0};

din_start = 2'b00;

din_end = 16'b00000000_00100000;

UG-01088

2014.12.15

40GbE IP Core Without Adapters

3-13

Functional Description

Altera Corporation