Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 171

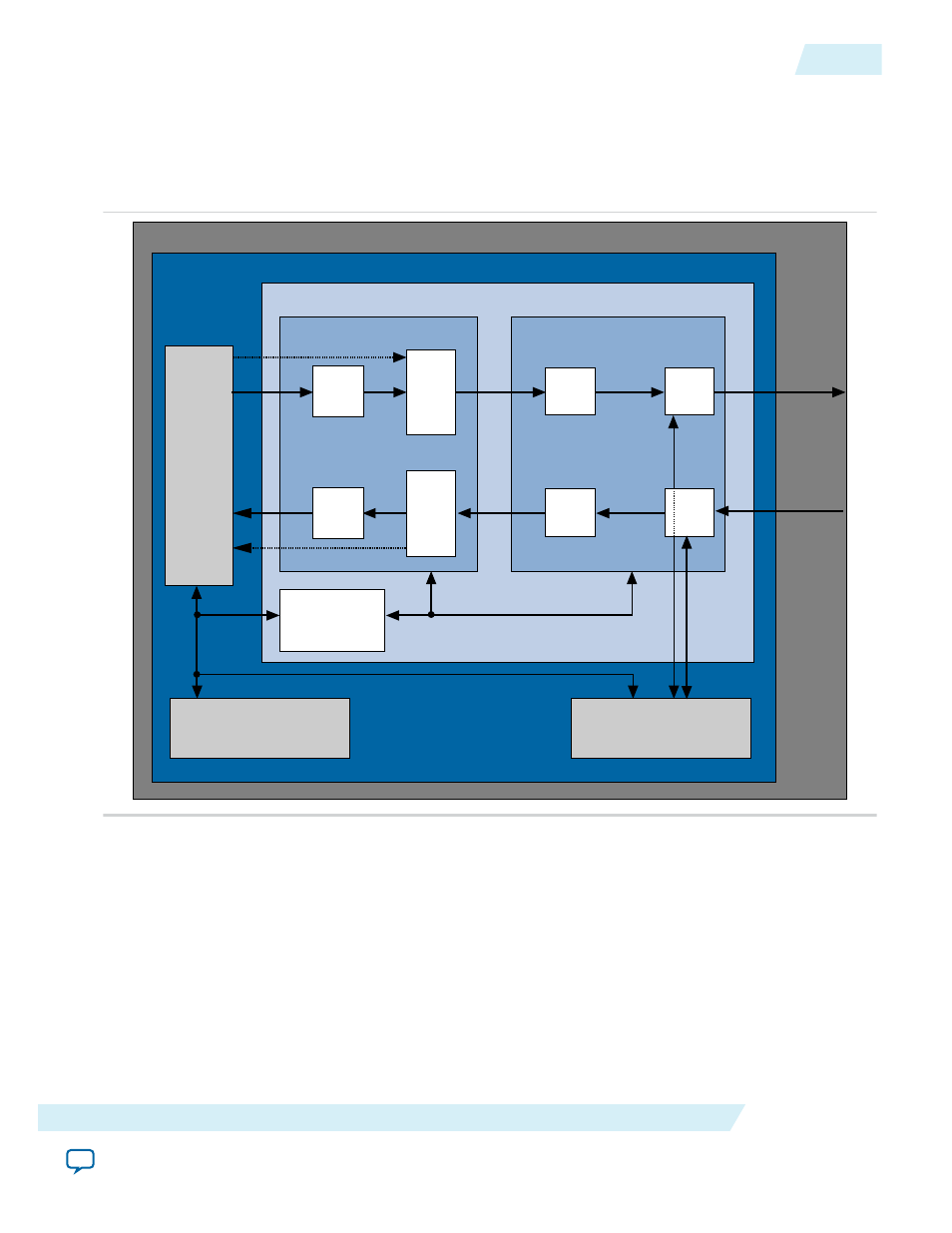

Figure A-2: High Level Block Diagram for the 40GBASE-KR4 Example Design

High level block diagram for 40GBASE-KR4 example designs. You can generate a 40GBASE-KR4

example design for any 40GBASE-KR4 IP core variation that includes both MAC and PHY components,

does not have Synchronous Ethernet support, does not have the link training microrporcoessor interface,

and has RX equalization enabled. Variations that meet these criteria can be with or without adapters,

unlike the testbench, which is available only for variations with adapters.

40GBASE-KR4 40Gbs Ethernet MAC and PHY MegaCore Function

40GBASE-KR4 40-Gbps Ethernet Example Design

Altera FPGA

Client

Logic

(pkt

gen/check)

TX

FIFO

TX

MAC

RX

MAC

40-GbE MAC

PMA

PMA

PCS

Transceiver PHY

TX

Adapter

PCS

XLGMII w/data_valid signal

or CGMII w/data_valid signal

4 x 40 bits or

10 x 40 bits

XLAUI: 4 x 10.3125 Gbps or

CAUI: 10 x 10.3125 Gbps

Custom Streaming

Avalon-ST

Avalon-ST

Control and

Status Interface

Avalon-MM

RX

Adapter

Custom Streaming

Reconfiguration

Bundle

JTAG Avalon-MM Master

Altera’s example design includes either the 40GbE or 100GbE IP core. Client logic connects to the TX and

RX Ethernet MAC. The TX and RX logic in the MAC includes an optional adapter which is available for

both the 40GbE and 100GbE IP cores. When you use the optional adapter, the start of packet (SOP) is

always in the most significant word (64 bits) of the bus, simplifying the interpretation of incoming data.

When the configuration includes adapters, the interface between the client logic and TX and RX FIFOs

uses the Avalon-ST protocol. Without adapters, the interface between client logic and the TX and RX

MAC is a custom streaming interface.

The bandwidth for the two versions is the same. However, the version without adapters achieves this

bandwidth with a narrower bus, because it does not restrict the SOP to the most significant word of the

bus. In the version without adapters, the SOP can be in the MSB of any word. The penalty for the less

restrictive positioning of the SOP is a data stream which is more difficult to interpret.

UG-01088

2014.12.15

40-100GbE IP Core Example Design

A-3

40-100GbE IP Core Example Design

Altera Corporation