Pcs hardware error register, Ber monitor register – Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 134

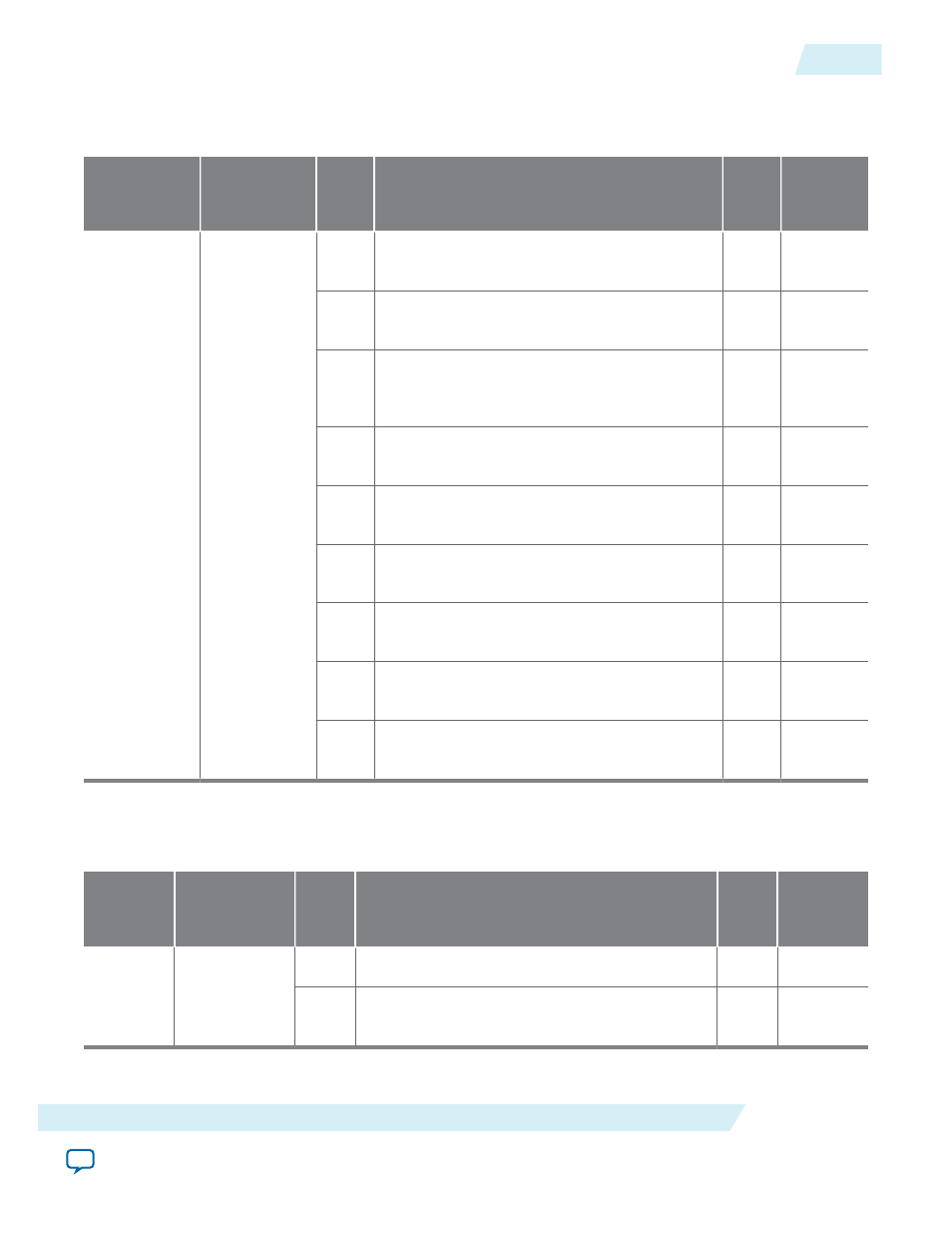

PCS Hardware Error Register

Table 3-30: PCS Hardware Error Register

Address

Name

Bit

Description

HW

Reset

Value

Access

0x017

PCS_HW_ERR

[8]

When asserted, indicates a RX phase compensa‐

tion error.

1’b0

R

[7]

When asserted, indicates a TX phase compensa‐

tion error.

1’b0

R

[6]

When asserted, indicates a deskew failure

suggesting a problem with the remote

transmitter.

1’b0

R

[5]

When asserted, indicates a parity error in the RX

lanes (RXL) section.

1’b0

R

[4]

When asserted, indicates a RX deskew FIFO

buffer underflow error.

1’b0

R

[3]

When asserted, indicates a RX deskew FIFO

buffer overflow error.

1’b0

R

[2]

When asserted, indicates a parity error in the TX

lanes (TXL) section.

1’b0

R

[1]

When asserted, indicates a TX deskew FIFO

buffer underflow error.

1’b0

R

[0]

When asserted, indicates a TX deskew FIFO

buffer overflow error.

1’b0

R

BER Monitor Register

Table 3-31: BER Monitor Register—Offset 0x018

Address

Name

Bit

Description

HW

Reset

Value

Access

0x018

BER_MONITOR

[1]

This bit enables the BER monitor.

1’b0

RW

[0]

When asserted by the BER monitor block, this bit

indicates the PCS is recording a high BER.

1’b0

R

UG-01088

2014.12.15

PCS Hardware Error Register

3-87

Functional Description

Altera Corporation