Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 11

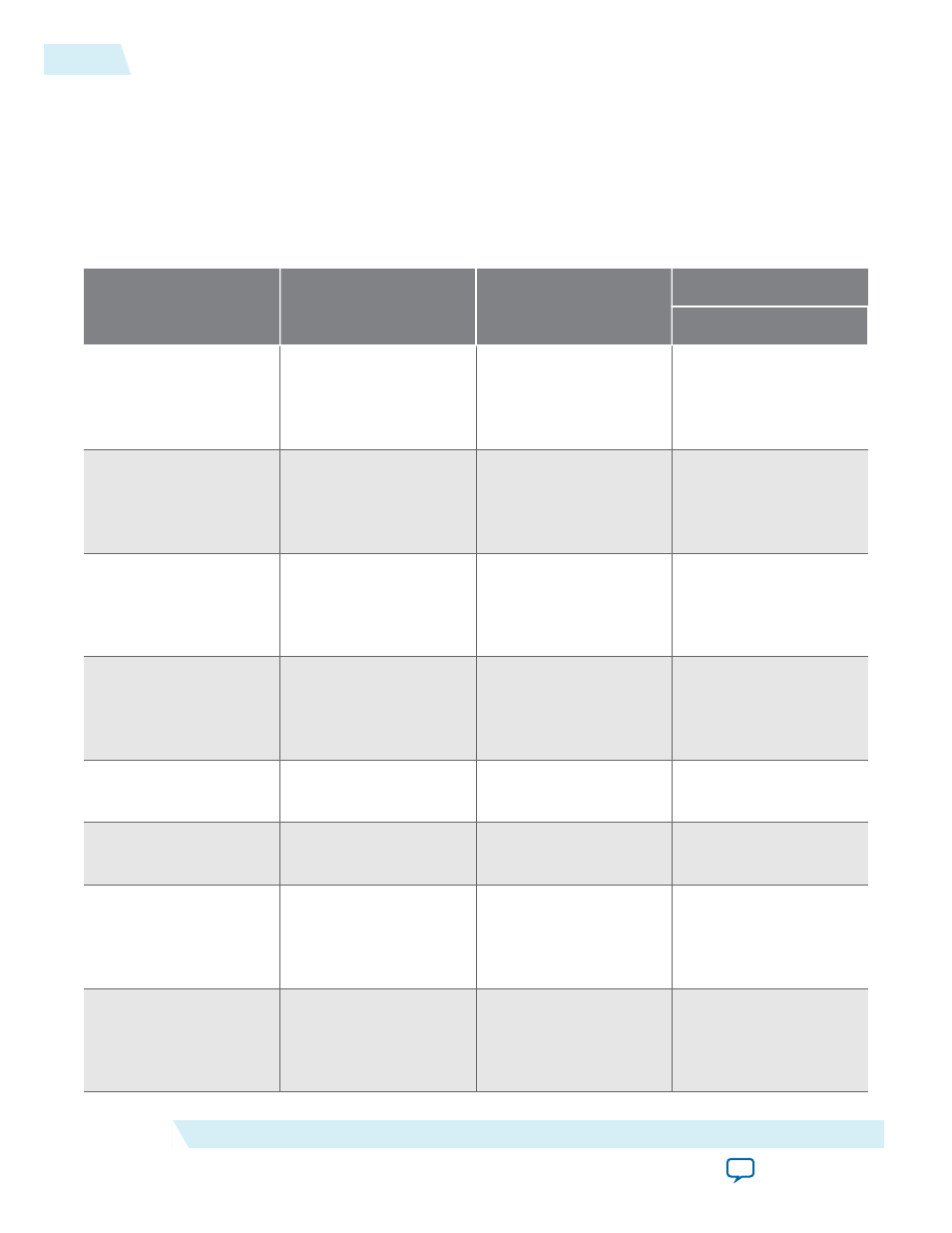

Table 1-4: 40GbE IP Core FPGA Resource Utilization in Stratix V and Arria V GZ Devices

Lists the resources and expected performance for selected variations of the 40GbE IP cores in an Arria V GZ or

Stratix V device. The results were obtained using the Quartus II software v13.1 for a Stratix V 5SGXEA7N2F45C2

device.

• Top-level modules are in bold.

• The numbers of ALMs and logic registers are rounded up to the nearest 100.

• The numbers of ALMs, before rounding, are the ALMs needed numbers from the Quartus II Fitter Report.

Module

ALMs

Logic Registers

Memory

M20K

MAC&PHY with

Avalon-ST client

interface without

statistics counters

13600

23500

9

MAC&PHY with

Avalon-ST client

interface and with

statistics counters

17700

30900

9

MAC with Avalon-ST

client interface

without statistics

counters

7100

15000

9

MAC with Avalon-ST

client interface and

with statistics

counters

11300

22300

9

• alt_e40_adapter_

rx:adapter_rx

500

900

0

• alt_e40_adapter_

tx:adapter_tx

300

700

0

MAC with custom

streaming client

interface without

statistics counters

6200

13400

9

MAC with custom

streaming client

interface and with

statistics counters

10400

20700

9

1-8

Resource Utilization for 40GbE IP Cores

UG-01088

2014.12.15

Altera Corporation

About the 40- and 100-Gbps Ethernet MAC and PHY MegaCore Function