Congestion and flow control using pause frames, Congestion and flow control using pause frames -33 – Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 80

Congestion and Flow Control Using Pause Frames

The 40-100GbE IP core provides flow control to reduce congestion at the local or remote link partner.

When either link partner experiences congestion, the respective transmit control sends pause frames. The

pause frame instructs the remote transmitter to stop sending data for the duration that the congested

receiver specified in an incoming XOFF frame.

When the IP core receives the XOFF pause control frame, if the following conditions all hold, the IP core

stops transmitting frames for a period equal to the pause quanta of the incoming pause frame. While

paused, the IP core does not transmit data but can transmit pause frames.

• The appropriate bit of the

RECEIVE_PAUSE_CONTROL

register has the value of 1.

• Address matching is positive.

The pause quanta can be configured in the pause quanta register of the device sending XOFF frames. If

the pause frame is received in the middle of a frame transmission, the transmitter finishes sending the

current frame and then suspends transmission for a period specified by the pause quanta. Data transmis‐

sion resumes when a pause frame with quanta of zero is received or when the timer has expired. The

pause quanta received overrides any counter currently stored. When more than one pause quanta is sent,

the value of the pause is set to the last quanta received.

XOFF pause frames stop the remote transmitter. XON pause frames let the remote transmitter resume

data transmission.

One pause quanta fraction is equivalent to 512 bit times, which equates to 512/64 (the width of the MAC

data bus), or eight system clock cycles.

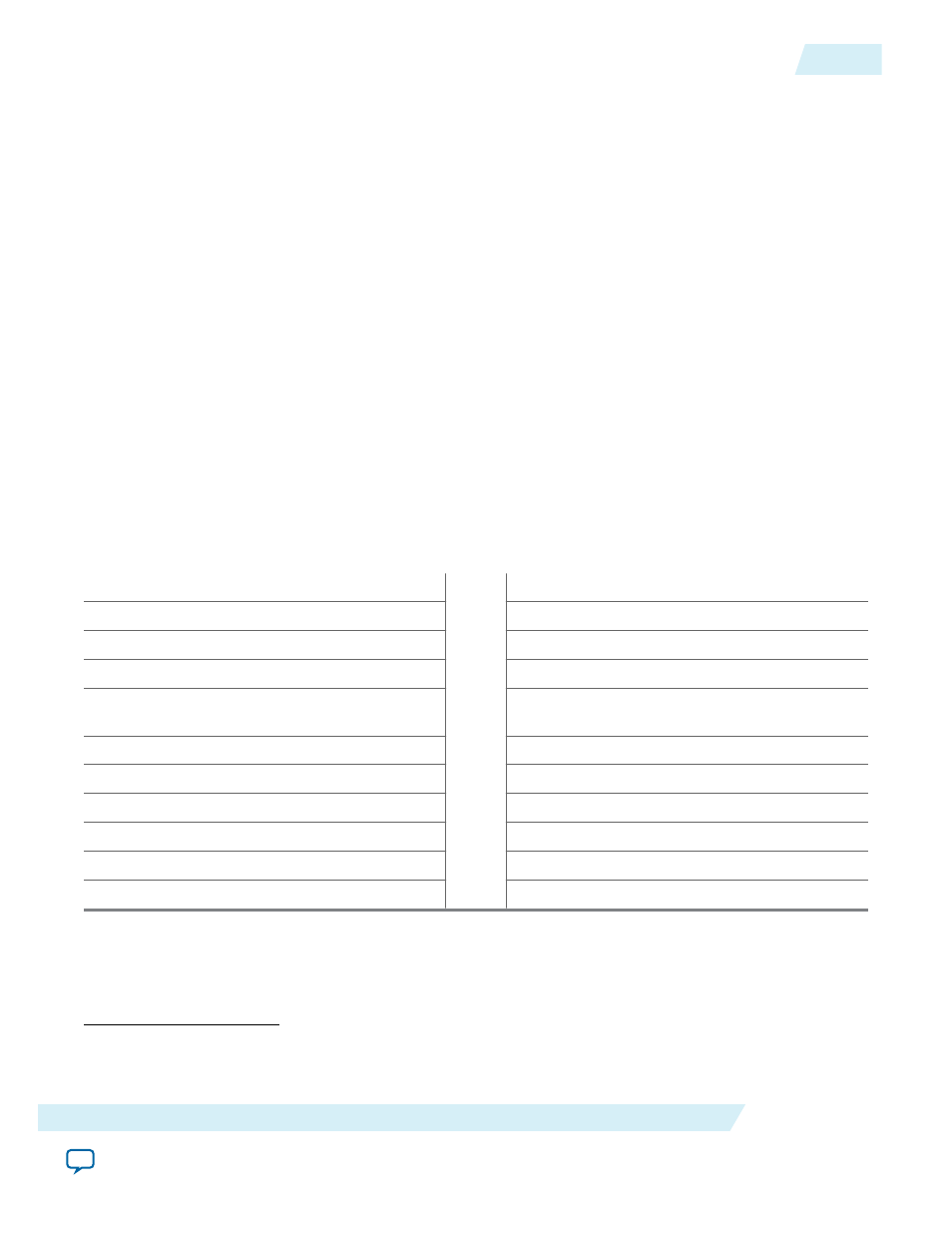

Figure 3-28: The XOFF and XON Pause Frames

XOFF Frame

XON Frame

START[7:0]

START[7:0]

PREAMBLE[47:0]

PREAMBLE[47:0]

SFD[7:0]

SFD[7:0]

DESTINATION ADDRESS[47:0] =

0x010000C28001

(10)

DESTINATION ADDRESS[47:0] =

0x010000C28001

SOURCE ADDRESS[47:0]

SOURCE ADDRESS[47:0]

TYPE[15:0] = 0x8808

TYPE[15:0] = 0x8808

OPCODE[15:0] = 0x001

OPCODE[15:0] = 0x001

PAUSE QUANTA[15:0] = 0xP1, 0xP2

(11)

PAUSE QUANTA[15:0] = 0x0000

PAD[335:0]

PAD[335:0]

CRC[31:0]

CRC[31:0]

(10)

This is a multicast destination address. You can use a unicast address if unicast addresses are enabled in the

pause register.

(11)

The bytes P1 and P2 are filled with the value configured in the

pause_quanta

register.

UG-01088

2014.12.15

Congestion and Flow Control Using Pause Frames

3-33

Functional Description

Altera Corporation