Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 83

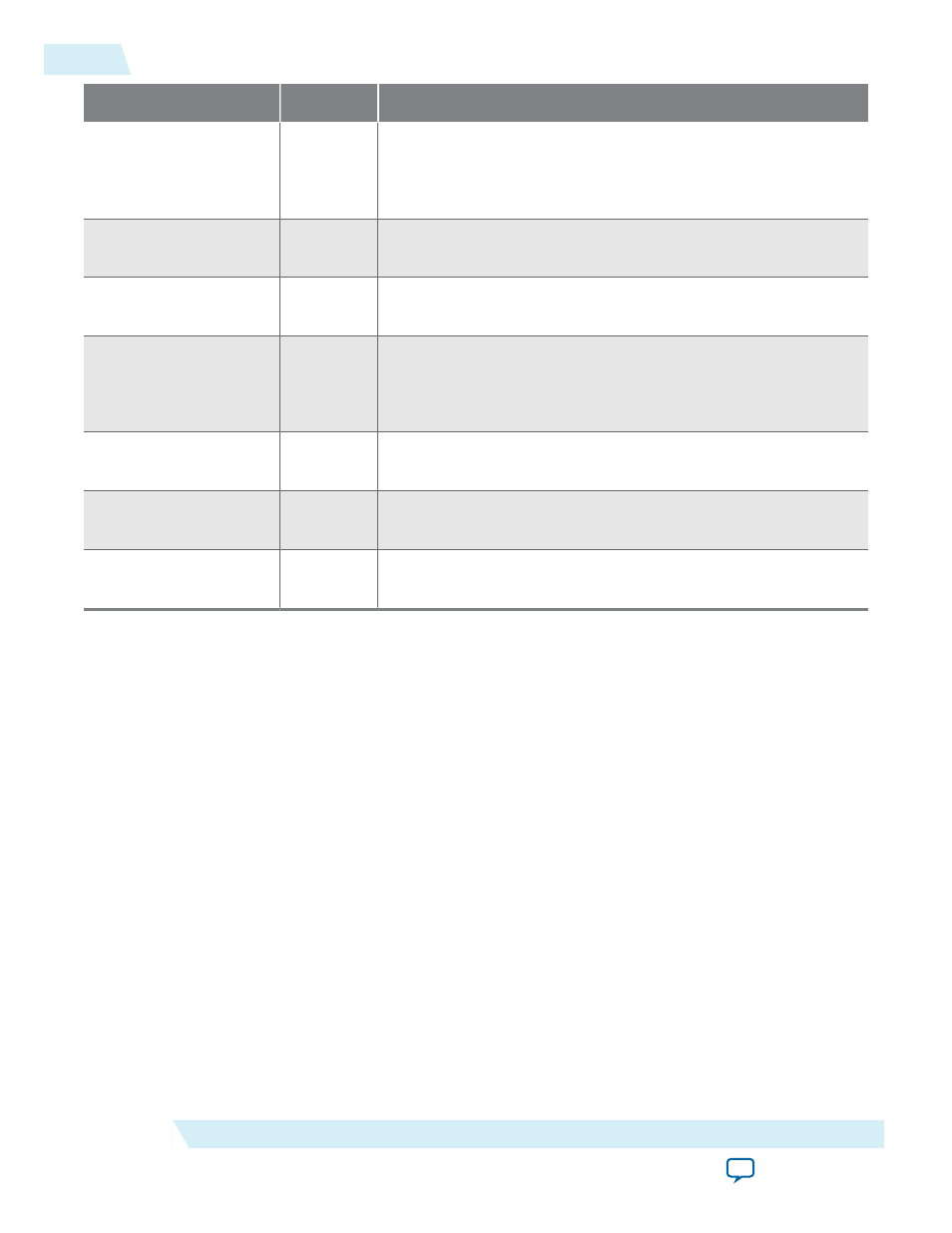

Signal Name

Direction

Description

pause_insert_mcast

Input

When asserted, specifies that the IP core should generate a pause

packet with the well-known multicast address of 01-80-C2-00-00-

01. If deasserted, the pause is generated with the specified MAC

address (

pause_insert_dst

), which is typically a unicast address.

pause_insert_dst

[47:0]

Input

Specifies the MAC address for a unicast pause.

pause_insert_src

[47:0]

Input

Specifies source address of the pause packet.

pause_match_from_rx

Output

Asserted to indicate an RX pause signal match. Used only when

RX configurations are instantiated. The IP core asserts this signal

when it receives a pause request with an address match, to signal

the TX MAC to throttle its transmissions on the Ethernet link.

pause_time_from_

rx[15:0]

Output

Asserted for RX pause time. Used only when RX configurations

are instantiated.

pause_match_to_tx

Input

Asserted to indicate a TX pause signal match. Used only when TX

configurations are instantiated.

pause_time_to_

tx[15:0]

Input

Asserted for TX pause time. Used only when TX configurations

are instantiated.

Related Information

•

Pause Control Frame and Non-Pause Control Frame Filtering and Forwarding

Information about enabling and disabling the pause packets pass-through.

•

You can access the pause functionality using the pause registers for any 40-100GbE IP core variation

that includes a MAC component. Values you program in the registers specify the pause quanta.

Pause Control Frame and Non‑Pause Control Frame Filtering and Forwarding

The 40GbE and 100GbE MAC IP cores can pass the pause packets through as normal traffic or drop the

pause control frames in the RX direction. You can enable and disable pass-through with the following

configuration control bits:

•

RX_FILTER_CTRL

bit [4] enables and disables pause filtering.

•

RX_FILTER_CTRL

bit [5] enables and disables control filtering.

By default, pass-through is disabled.

The following rules define pause control frames filtering control:

1. The

RX_FILTER_CTRL

register contains options to filter different packets types, such as runt packets,

FCS error packets, address mismatch packets, and so on, from the RX MAC. The

RX_FILTER_CTRL

register contains one bit to enable pause packet filtering and one bit to enable non-pause control

3-36

Pause Control Frame and Non‑Pause Control Frame Filtering and Forwarding

UG-01088

2014.12.15

Altera Corporation

Functional Description