Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 140

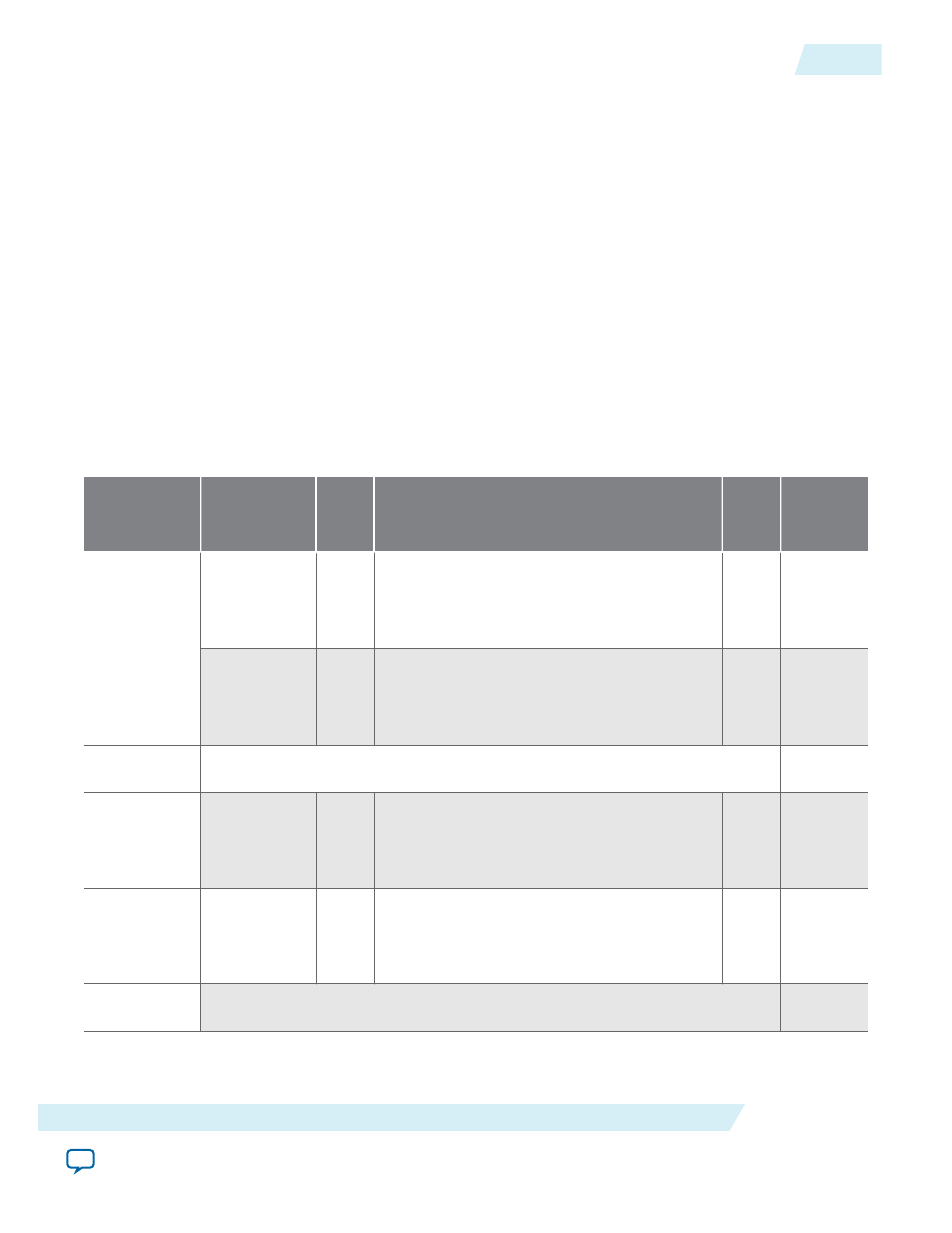

Table 3-40: 40-100GbE IP Core 40GBASE-KR4 Registers and Register Fields Not in 10GBASE-KR PHY IP Core

Documents the differences between the 10GBASE-KR PHY register definitions and the 40GBASE-KR4 registers

of the 40-100GbE IP core. All 10GBASE-KR PHY registers and register fields not listed in the table are available in

the 40GBASE-KR4 variations of the 40-100GbE IP core.

The 10GBASE-KR PHY register listings are available in the

appendix and in the

10GBASE-KR PHY Register Defintions section of the Backplane Ethernet 10GBASE-KR PHY IP Core with FEC

Option chapter of the Altera Transceiver PHY IP Core User Guide. The information in these two sources should be

identical. Refer to

Where the 10GBASE-KR PHY register definitions list 10GBASE-R, substitute 40GBASE-KR4 with auto-negotia‐

tion and link training both turned off, and where the 10GBASE-KR PHY register definitions list 10GBASE-KR

(except in the description of 0xCB[24:0]), substitute 40GBASE-KR4. Where a register field description in the

10GBASE-KR PHY register definitions refers to link training or FEC in the single-lane 10GBASE-KR PHY IP

core, substitute link training or FEC on Lane 0 of the 40GBASE-KR4 IP core variation. Where a register field

description in the 10GBASE-KR PHY register definitions refers to the Transceiver Reconfiguration IP core,

substitute the reconfiguration bundle.

To modify a field value in any 40GBASE-KR4 specific register, whether an underlying 10GBASE-KR PHY IP core

register or one of the registers defined in this table, you must perform a read-modify-write operation to ensure

you do not modify the values of any other fields in the register.

Address

Name

Bit

Description

HW

Reset

Value

Access

0x0B0

Force

Negotiate to

FEC Mode

[19]

When set to 1, forces the IP core to use FEC

mode regardless of the auto-negotiation result.

You must write the value of 1 to 0xB0[0] (reset

the sequencer) for this override to take effect.

1’b0

RW

FEC Block

Lock

[23:20

]

FEC Block Lock for lanes [3:0]: bit [20] is FEC

block lock for lane 0, bit [21] is FEC block lock

for lane 1, bit [22] is FEC block lock for lane 2,

and bit [23] is FEC block lock for lane 3.

4’b0

RO

0x0B5

Register 0xB2 refers to Lane 0. This register is the equivalent of register 0xB2 for

10GBASE-KR PHY Register Definitions

).

RW

0x0B6

KR4 FEC

Corrected

Blocks, Lane

1

[31:0] Maintains count of corrected FEC blocks on

Lane 1, saturating (not rolling over) at 2

32

-1.

Resets to 0 when read. Refer to Clause 74.8.4.1 of

IEEE Std 802.3ap-2007.

32'b0 RO

0x0B7

KR4 FEC

Uncorrected

Blocks, Lane

1

[31:0] Maintains count of uncorrected (uncorrectable)

FEC blocks on Lane 1, saturating (not rolling

over) at 2

32

-1. Resets to 0 when read. Refer to

Clause 74.8.4.2 of IEEE Std 802.3ap-2007.

32'b0 RO

0x0B8

This register is the equivalent of register 0xB2 for Lane 2. (Refer to

).

RW

UG-01088

2014.12.15

40GBASE-KR4 Registers

3-93

Functional Description

Altera Corporation