Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 182

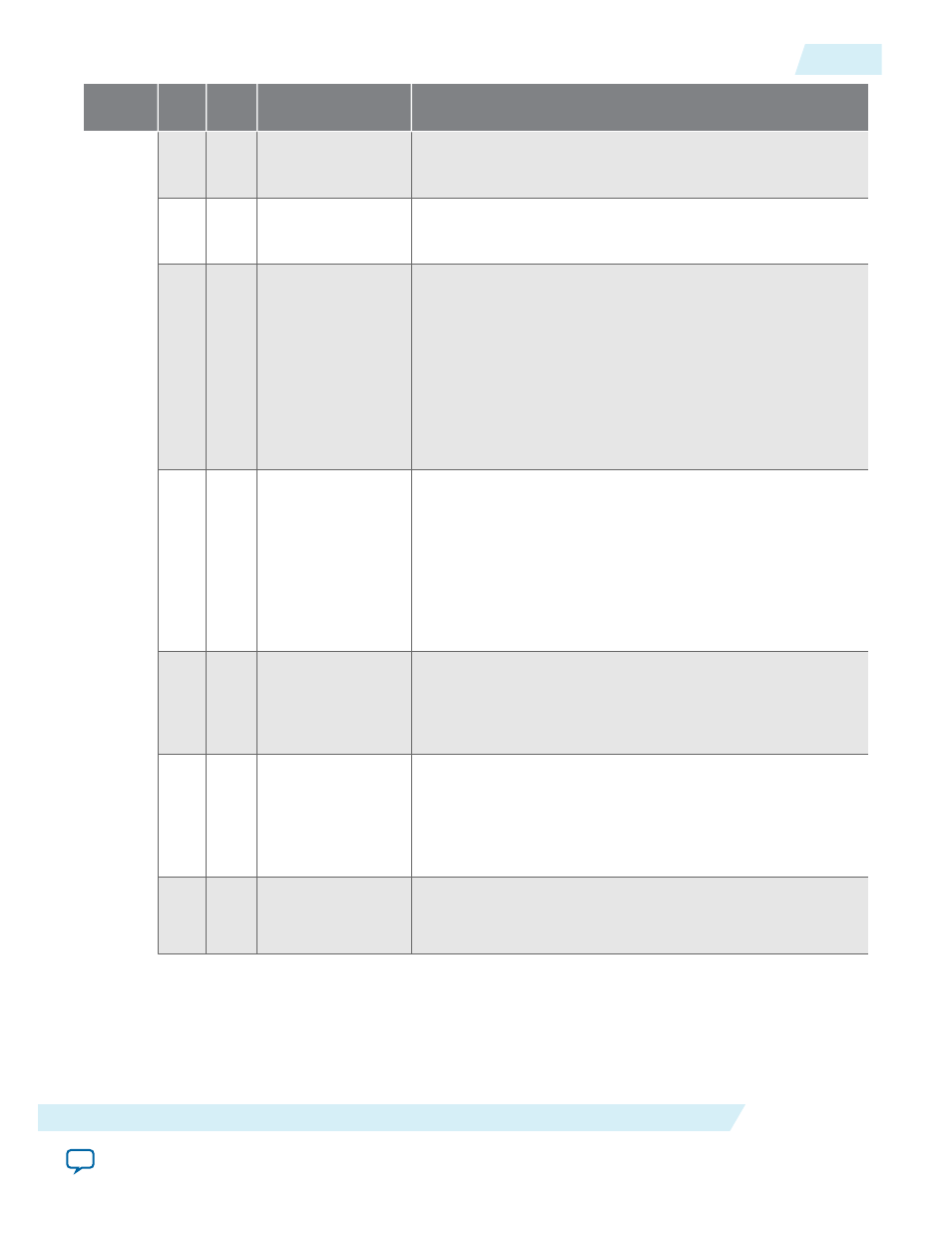

Word

Addr

Bit

R/W

Name

Description

7:4

RW

main_step_cnt

[3:0]

Specifies the number of equalization steps for each main tap

update. There are about 20 settings for the internal algorithm

to test. The valid range is 1-15. The default value is 4'b0010.

11:8 RW

prpo_step_cnt

[3:0]

Specifies the number of equalization steps for each pre- and

post- tap update. From 16-31 steps are possible. The default

value is 4'b0001.

14:12 RW

equal_cnt [2:0]

Adds hysteresis to the error count to avoid local minimums.

The default value is 3'b010. The following encodings are

defined:

• 3'b000: 0

• 3'b001: 1

• 3'b010: 2

• 3'b100: 4

• 3'b101: 8

• 3'b110: 16

15

RW

disable

initialize PMA on

max_wait_timeout

When set to 1, does not initialize the PMA V

OD

, pretap,

posttap values upon entry into the Training_Failure state as

defined in Figure 72-5 of Clause 72.6.10.4.3 of IEEE 802.3ap-

2007. This failure occurs when the

max_wait_timer_done

timeout is reached setting the

Link Training failure

bit

(0xD2[3]). Used during UNH-IOL testing.

When set to 0, initializes the PMA values upon entry into

Training_Failure state.

16

RW

Ovride LP Coef

enable

When set to 1, overrides the link partner's equalization

coefficients; software changes the update commands sent to

the link partner TX equalizer coefficients. When set to 0, uses

the Link Training logic to determine the link partner

coefficients. Used with 0xD1 bit-4 and 0xD4 bits[7:0].

17

RW

Ovride Local RX

Coef enable

When set to 1, overrides the local device equalization

coefficients generation protocol. When set, the software

changes the local TX equalizer coefficients. When set to 0,

uses the update command received from the link partner to

determine local device coefficients. Used with 0xD1 bit-8 and

0xD4 bits[23:16]. The default value is 1.

19:18 RM

W

Reserved

You should not modify these bits. To update this register,

first read the value of this register then change only the value

for bits that are not reserved.

UG-01088

2014.12.15

10GBASE-KR PHY Register Definitions

C-9

10GBASE-KR Registers

Altera Corporation