Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 176

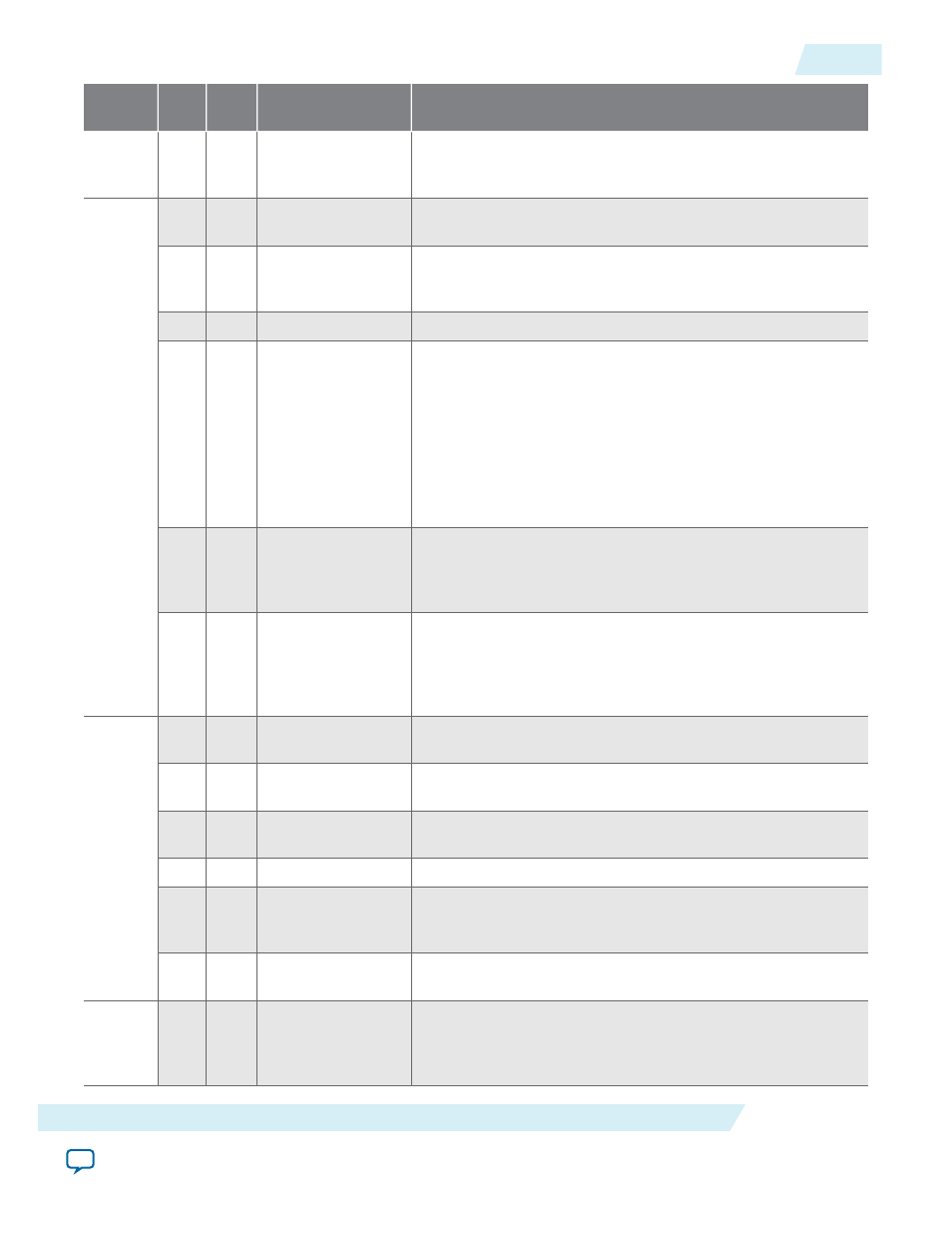

Word

Addr

Bit

R/W

Name

Description

18

RW

Assert KR FEC

Request

When set to 1, indicates that the core is requesting the FEC

ability. When this bit changes, you must assert the

Reset SEQ

bit (0xB0[0]) to renegotiate with the new value.

0xB1

0

R

SEQ Link Ready

When asserted, the sequencer is indicating that the link is

ready.

1

R

SEQ AN timeout

When asserted, the sequencer has had an Auto-Negotiation

timeout. This bit is latched and is reset when the sequencer

restarts Auto-Negotiation.

2

R

SEQ LT timeout

When set, indicates that the Sequencer has had a timeout.

13:8 R

SEQ Reconfig

Mode[5:0]

Specifies the Sequencer mode for PCS reconfiguration. The

following modes are defined:

• Bit 8, mode[0]: AN mode

• Bit 9, mode[1]: LT Mode

• Bit 10, mode[2]: 10G data mode

• Bit 11, mode[3]: Gige data mode

• Bit 12, mode[4]: Reserved for XAUI

• Bit13, mode[5]: 10G FEC mode

16

R

KR FEC Ability

Indicates whether or not the 10GBASE-KR PHY supports

FEC. For more information, refer to the FEC variable

FEC_

Enable

as defined in Clause 74.8.2 and 10GBASE-KR PMD

control register bit (1.171.0) IEEE 802.3ap-2007.

17

R

Enable KR FEC

Error Indication

Ability

When set to 1, indicates that the 10GBASE-KR PHY is

capable of reporting FEC decoding errors to the PCS. For

more information, refer to the KR FEC variable

FEC_enable_

Error_to_PCS

and 10GBASE-KR PMD control register bit

(1.171.1) as defined in Clause 74.8.3 of IEEE 302.3ap-2007.

0xB2

0

RW

FEC TX trans

error

When asserted, indicates that the error insertion feature in

the FEC Transcoder is enabled.

1

RW

FEC TX burst

error

When asserted, indicates that the error insertion feature in

the FEC Encoder is enabled.

5:2

RW

FEC TX burst

length

Specifies the length of the error burst. Values 1-16 are

available.

10:6

Reserved

11

RWS

C

FEC TX Error

Insert

Writing a 1 inserts 1 error pulse into the TX FEC depending

on the Transcoder and Burst error settings. Software clears

this register.

31:15 RWS

C

Reserved

0xB3 31:0 RSC

FEC Corrected

Blocks

Counts the number of corrected FEC blocks. Resets to 0

when read. Otherwise, it holds at the maximum count and

does not roll over. Refer to Clause 74.8.4.1 of IEEE 802.3ap-

2000 for details.

UG-01088

2014.12.15

10GBASE-KR PHY Register Definitions

C-3

10GBASE-KR Registers

Altera Corporation