Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 112

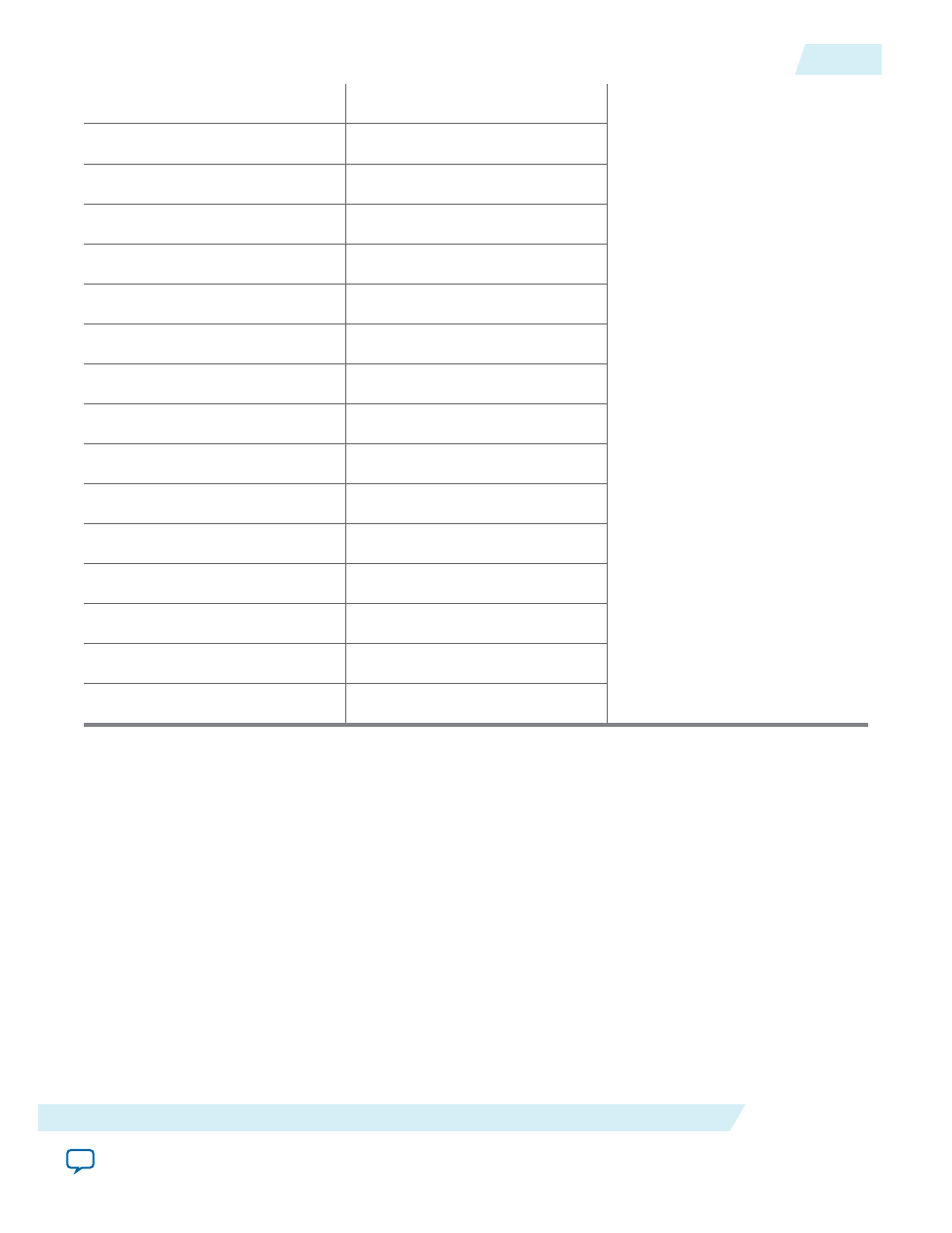

rc_busy[3:0]

Input

40GBASE-KR4 reconfiguration

interface. These signals are

present only in 40GBASE-KR4

variations for which you turn on

Enable KR4 Reconfiguration.

All 40GBASE-KR4 variations are

in Duplex mode.

The

lt_start_rc

,

main_rc

,

post_rc

,

pre_rc

, and

tap_to_

upd

signals are present only if

you turn on Enable Link

Training.

The

dfe_start_rc

,

dfe_mode

,

ctle_start_rc

,

ctle_rc

, and

ctle_mode

signals are present

only if you turn on Enable RX

equalization.

lt_start_rc[3:0]

Output

main_rc[23:0]

Output

post_rc[19:0]

Output

pre_rc[15:0]

Output

tap_to_upd[11:0]

Output

seq_start_rc[3:0]

Output

dfe_start_rc[3:0]

Output

dfe_mode[7:0]

Output

ctle_start_rc[3:0]

Output

ctle_rc[15:0]

Output

ctle_mode[7:0]

Output

pcs_mode_rc[5:0]

Output

en_lcl_rxeq[3:0]

Output

rxeq_done[3:0]

Input

reco_mif_done

Input

Related Information

•

Overview of IP core reset access. Includes list of reset signals and recommended reset sequence.

•

Transceiver PHY Serial Data Interface

on page 3-45

•

MAC to PHY Connection Interface

on page 3-43

Describes the

tx_lanes_stable

PHY output signal.

•

on page 3-51

Overview of IP core clocks. Includes list of clock signals and recommended and required frequencies.

•

40-100GbE IP Core TX Data Bus Without Adapters (Custom Streaming Interface)

•

Pause Control and Generation Interface

on page 3-35

•

Link Fault Signaling Interface

•

•

on page 3-108

•

on page 3-43

Describes the

lanes_deskewed

PHY output signal.

UG-01088

2014.12.15

Signals of MAC and PHY Variations Without Adapters

3-65

Functional Description

Altera Corporation