Testbenches without adapters, Testbenches without adapters -18 – Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 40

7. At marker 7, the 40GbE IP core asserts

l4_rx_valid

, indicating that the it has valid data to send to the

client on

l4_rx_data[255:0]

.

8. At marker 8, the 40GbE IP core deasserts

l4_rx_valid

, indicating that the 40GbE IP core does not

have new valid data to send to the client on

l4_rx_data[255:0]

.

l4_rx_data[255:0]

remains

unchanged for a second cycle.

9. At marker 9, the IP core asserts

l4_rx_endofpacket

, indicating the end of the RX packet.

l4_rx_empty[4:0]

has a value of 0x1D, indicating that 29 least significant bytes of the last cycle of the

RX packet empty.

Note: The ready latency on the TX client interface with adapters is 0.

Related Information

For more information about the Avalon-ST protocol.

Testbenches without Adapters

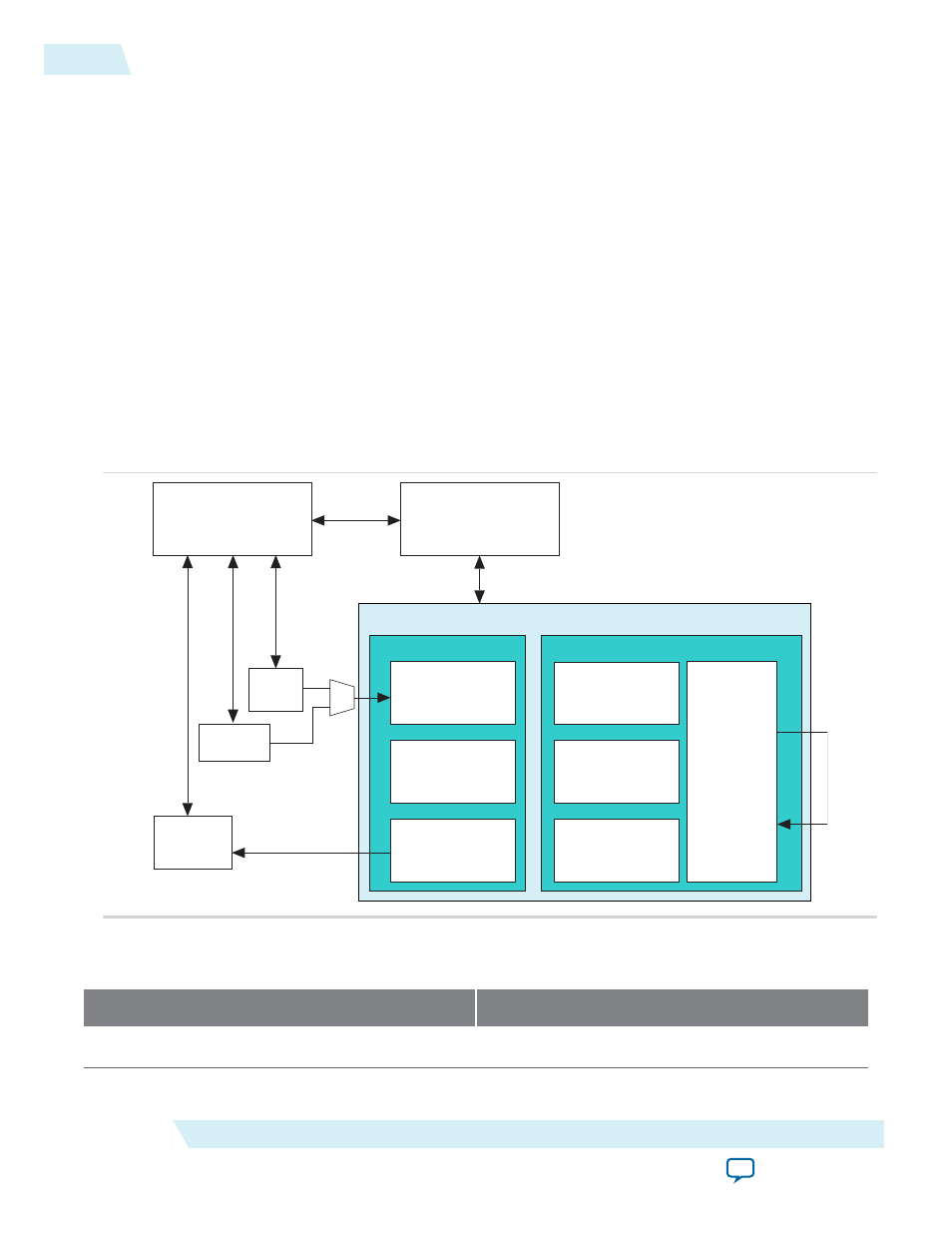

Figure 2-6: 40-100GbE IP Core Testbench Without Adapters

Illustrates the top-level modules of the 40GbE and 100GbE example testbenches that do not use adapters.

In the file names, * denotes 40 for 40GbE IP cores and 100 for 100GbE IP cores.

Transmit MAC

(alt_e*_mac_tx)

CSR MAC

(alt_e*_mac_csr)

Receive MAC

(alt_e*_mac_rx)

Transmit PCS

(alt_e*_pcs_tx)

PHY CSR

(alt_e*_phy_csr)

Receive PCS

(alt_e*_pcs_rx)

PMA

(alt_e*_pma)

MAC (alt_e*_mac)

PHY Core (alt_e*_phy)

40GbE and 100GbE MegaCore Function without Adapter (alt_e*)

Packet

Generator

Packet

Checker

Sample

ROM

Test Controller

& Test Result Checker

Memory Map Register

Read/Write Handler

Table 2-7: 40-100GbE IP Core Testbench Without Adapters File Descriptions

Lists the key files that implement the example testbenches.

File Names

Description

Testbench and Simulation Files

2-18

Testbenches without Adapters

UG-01088

2014.12.15

Altera Corporation

Getting Started