40gbase-kr4 microprocessor interface – Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 96

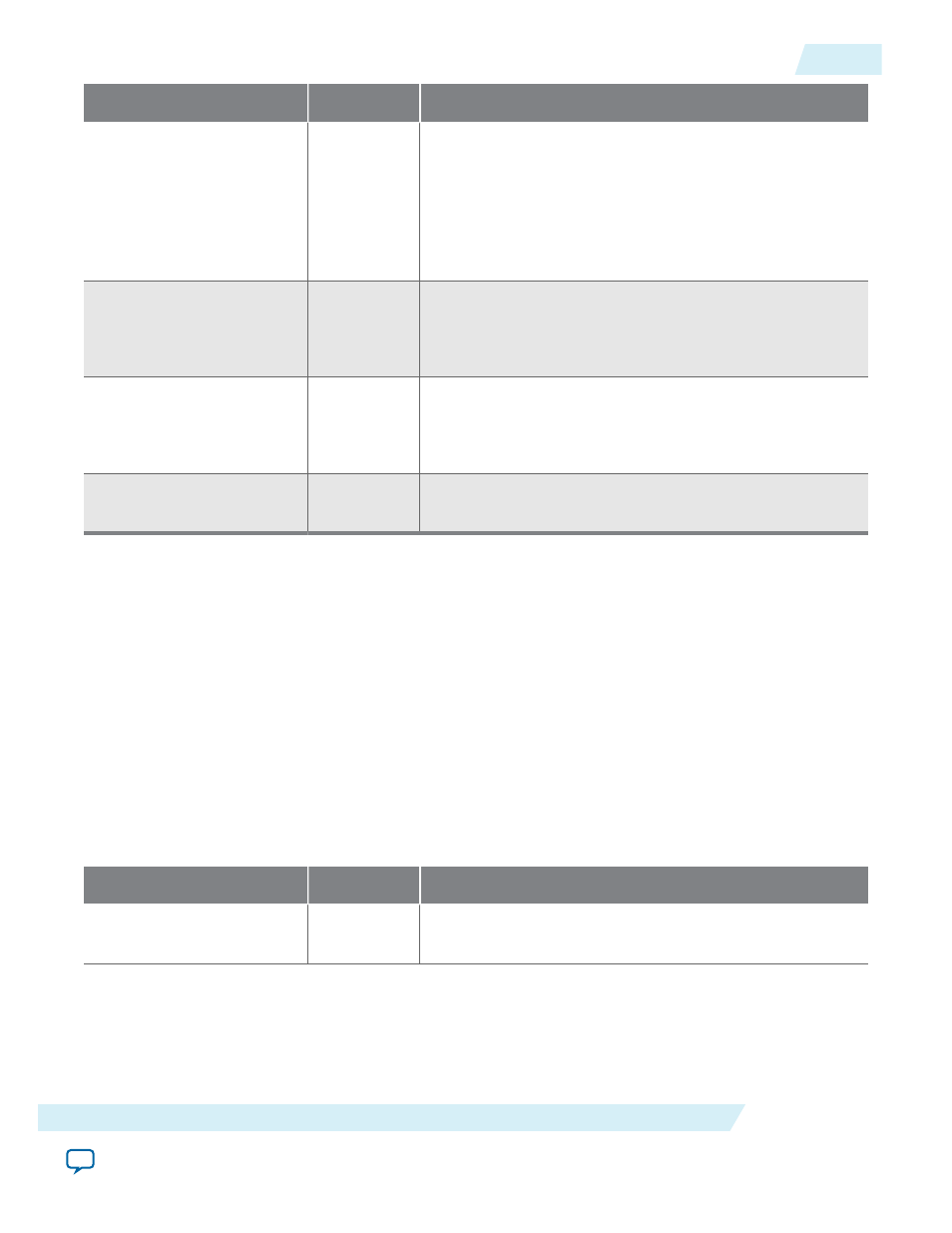

Signal Name

Direction

Description

pcs_mode_rc[5:0]

Output

Specifies the PCS mode for reconfiguration. Has the

following valid values:

• b'000001: auto-negotiation mode

• b'000010: link training mode

• b'100000: data mode (normal operation)

Other values are not valid for the 40GBASE-KR4 IP core.

en_lcl_rxeq[3:0]

Output

When a bit is asserted, it signals that an additional custom

RX equalization is enabled for the corresponding lane. The

bits are identical to the Link Trained status bits 0xD2 [0],

[8], [16], and [24].

rxeq_done[3:0]

Input

When asserted, indicates that custom RX equalization is

complete. The PHY IP core ANDs each bit of this signal

with

rx_trained

from the Training State Diagram for the

corresponding lane.

reco_mif_done

Input

Reset signal the user logic asserts after completing MIF

programming.

Related Information

40-100GbE IP Core Example Design

The 40GBASE-KR4 example design, specifically the reconfiguration bundle and its connections to the IP

core, provide an example of how to coordinate use of the transceiver reconfiguration interface and the

40GBASE-KR4 specific reconfiguration interface to your 40GBASE-KR4 IP core.

40GBASE-KR4 Microprocessor Interface

The optional embedded processor interface signals allow you to use the embedded processor mode of

Link Training. This mode overrides the TX adaptation algorithm and allows an embedded processor to

initialize the link.

Table 3-14: 40GBASE-KR4 Microprocessor Interface Signals

Signals with a width of 4 x n are divided into fields of width n. Bits [n-1:0] refer to Lane 0, bits [2n-1:n] refer to

Lane 1, bits [3n-1:2n] refer to Lane 2, and bits [4n-1:3n] refer to Lane 3. These signals are only available if you turn

on Enable microprocessor interface.

Signal Name

Direction

Description

upi_mode_en[3:0]

Input

When a bit is asserted, enables embedded processor mode

on the corresponding lane.

UG-01088

2014.12.15

40GBASE-KR4 Microprocessor Interface

3-49

Functional Description

Altera Corporation