Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 129

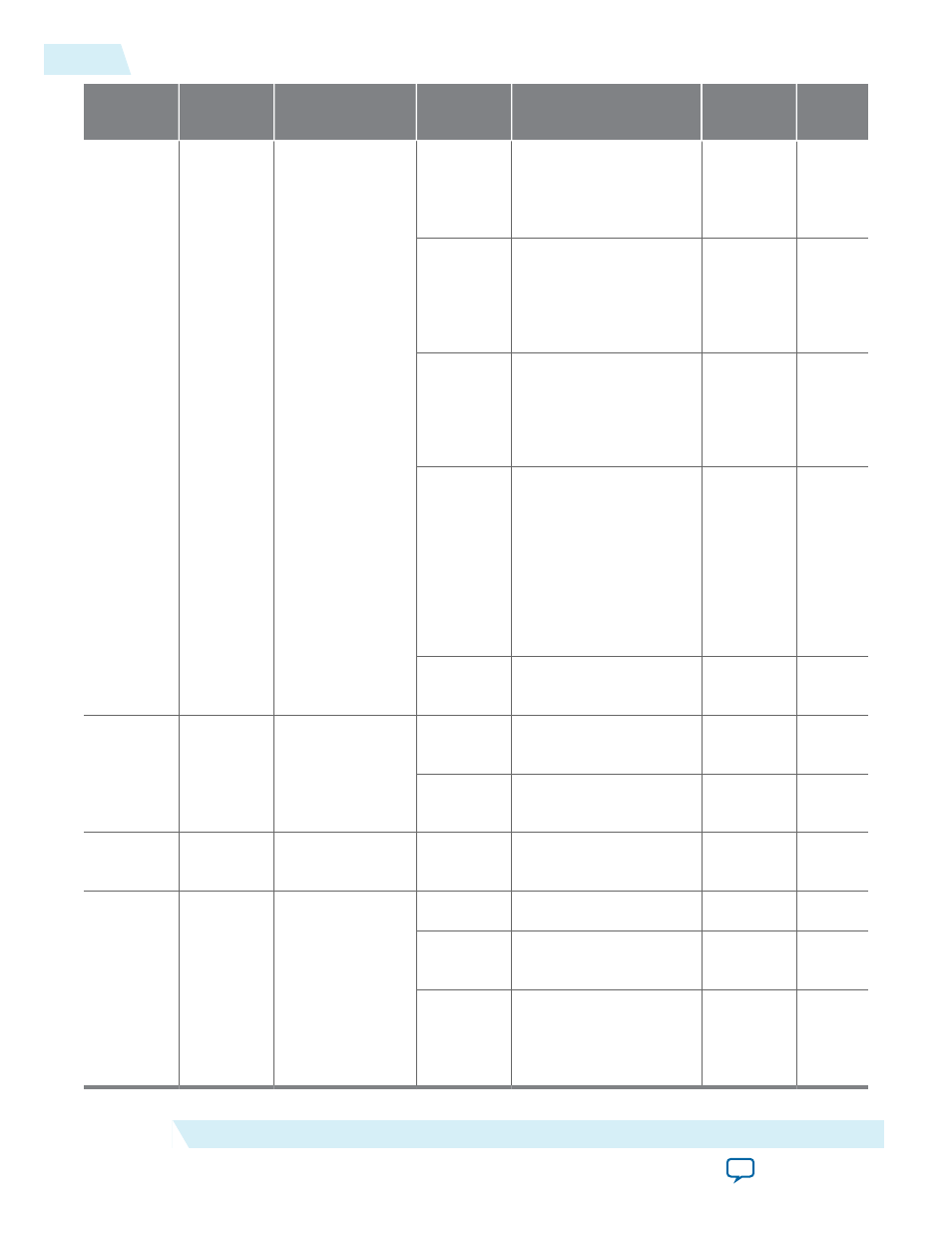

Address

Name

Applicable

Device(s)

Bit

Description

HW Reset

Value

Access

0x007

GX_CTRL1

Stratix IV

[31]

When set, places the

transceiver in Internal

serial loopback, from TX

to RX.

1’b0

RW

[30]

When asserted, the

transceiver channel’s

analog settings are read

on the rising edge of

clk_

status

.

1’b0

RW

[29]

When asserted, the

transceiver channel’s

analog settings are

written on rising edge of

clk_status

.

1’b0

RW

[28:4]

Specifies the analog

settings to write. Refer to

the following table for the

register fields which are

read on

GX_

REPLY[

24:0]

. Bits[28:4]

of this register

correspond to bits[24:0]

of the

GX_REPLY

register.

0x000000

RW

[3:0]

Specifies the logical

channel to select [0–9].

0x0

RW

0x008

GX_CTRL2

Arria V GZ,

Stratix IV, and

Stratix V

[1]

Specifies bit error inject

position 1 on rising edge.

1’b0

RW

[0]

Specifies bit error inject

position 0 on rising edge.

1’b0

RW

0x009

—

Arria V GZ and

Stratix V

–

Reserved.

—

—

0x009

GX_REPLY

Stratix IV

[26]

Reserved.

0

R

[25]

When asserted, indicates

that read data is valid.

1’b0

R

[24:0]

Contains the analog

settings reported in the

previous read of

GX_

CTRL1[28:4]

.

0x020080

R

3-82

Transceiver PHY Control and Status Registers

UG-01088

2014.12.15

Altera Corporation

Functional Description