Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 97

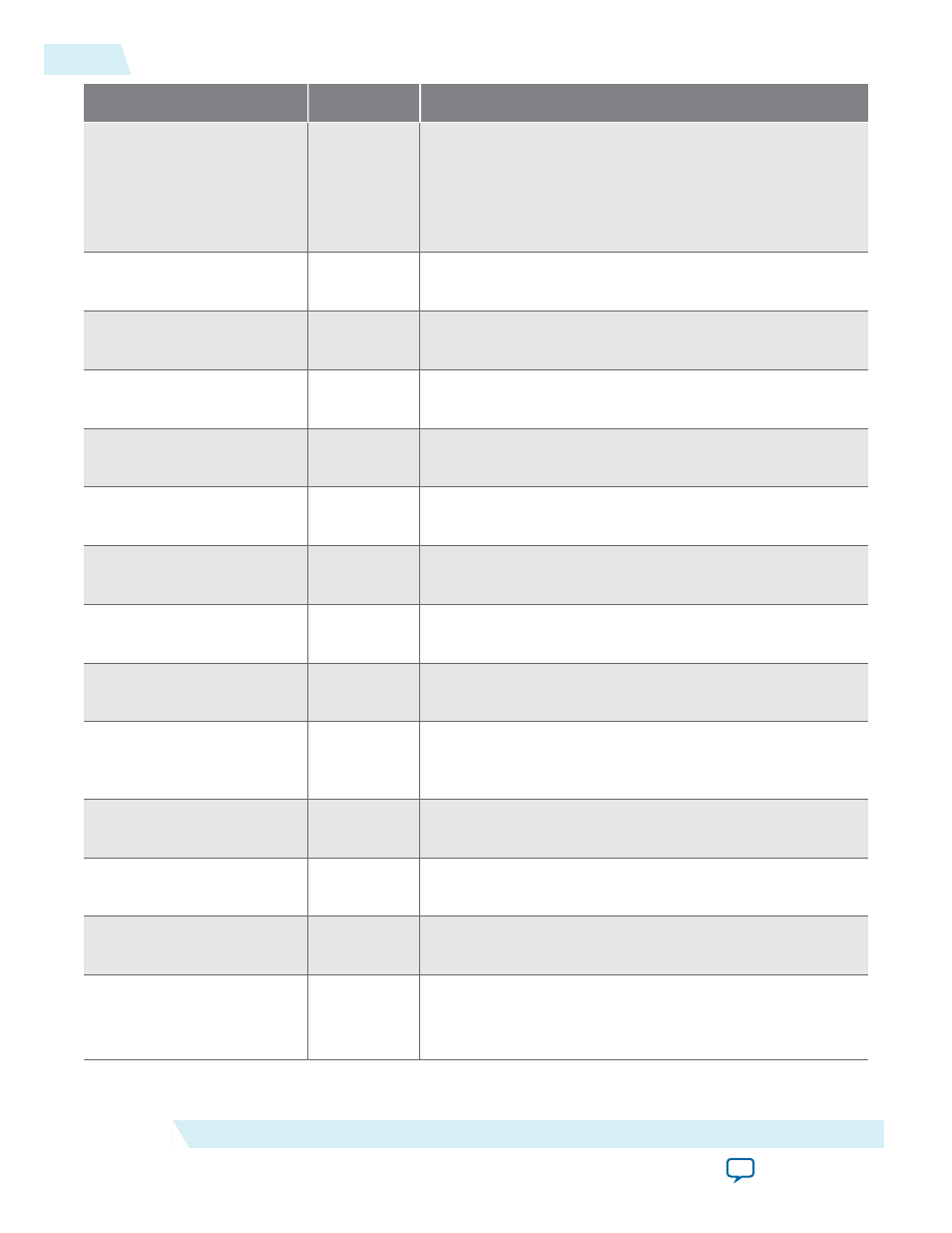

Signal Name

Direction

Description

upi_adj[7:0]

Input

Selects the active tap for the corresponding lane. Each lane's

field has the following valid values:

• 2'b01: main tap

• 2'b10: post-tap

• 2'b11: pre-tap

upi_inc[3:0]

Input

When a bit is asserted, sends the increment command for

the corresponding lane.

upi_dec[3:0]

Input

When a bit is asserted, sends the decrement command for

the corresponding lane.

upi_pre[3:0]

Input

When a bit is asserted, sends the preset command for the

corresponding lane.

upi_init[3:0]

Input

When a bit is asserted, sends the initialize command for the

corresponding lane.

upi_st_bert[3:0]

Input

When a bit is asserted, starts the BER timer for the

corresponding lane.

upi_train_err[3:0]

Input

When a bit is asserted, indicates a training error on the

corresponding lane.

upi_lock_err[3:0]

Input

When a bit is asserted, indicates a training frame lock error

on the corresponding lane.

upi_rx_trained[3:0]

Input

When a bit is asserted, the RX interface for the

corresponding lane is trained.

upo_enable[3:0]

Output

When a bit is asserted, indicates that the IP core is ready to

receive commands from the embedded processor for the

corresponding lane.

upo_frame_lock[3:0]

Output

When a bit is asserted, indicates the receiver has achieved

training frame lock on the corresponding lane.

upo_cm_done[3:0]

Output

When a bit is asserted, indicates the master state machine

handshake for the corresponding lane is complete.

upo_bert_done[3:0]

Output

When a bit is asserted, indicates the BER timing for the

corresponding lane is at its maximum count.

upo_ber_cnt[4*<bcw>-

1:0]

(width varies with

<bcw> = BER counter

width)

Output

Each four-bit field holds the current BER count for the

corresponding lane.

3-50

40GBASE-KR4 Microprocessor Interface

UG-01088

2014.12.15

Altera Corporation

Functional Description