Mac and phy reset registers – Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 136

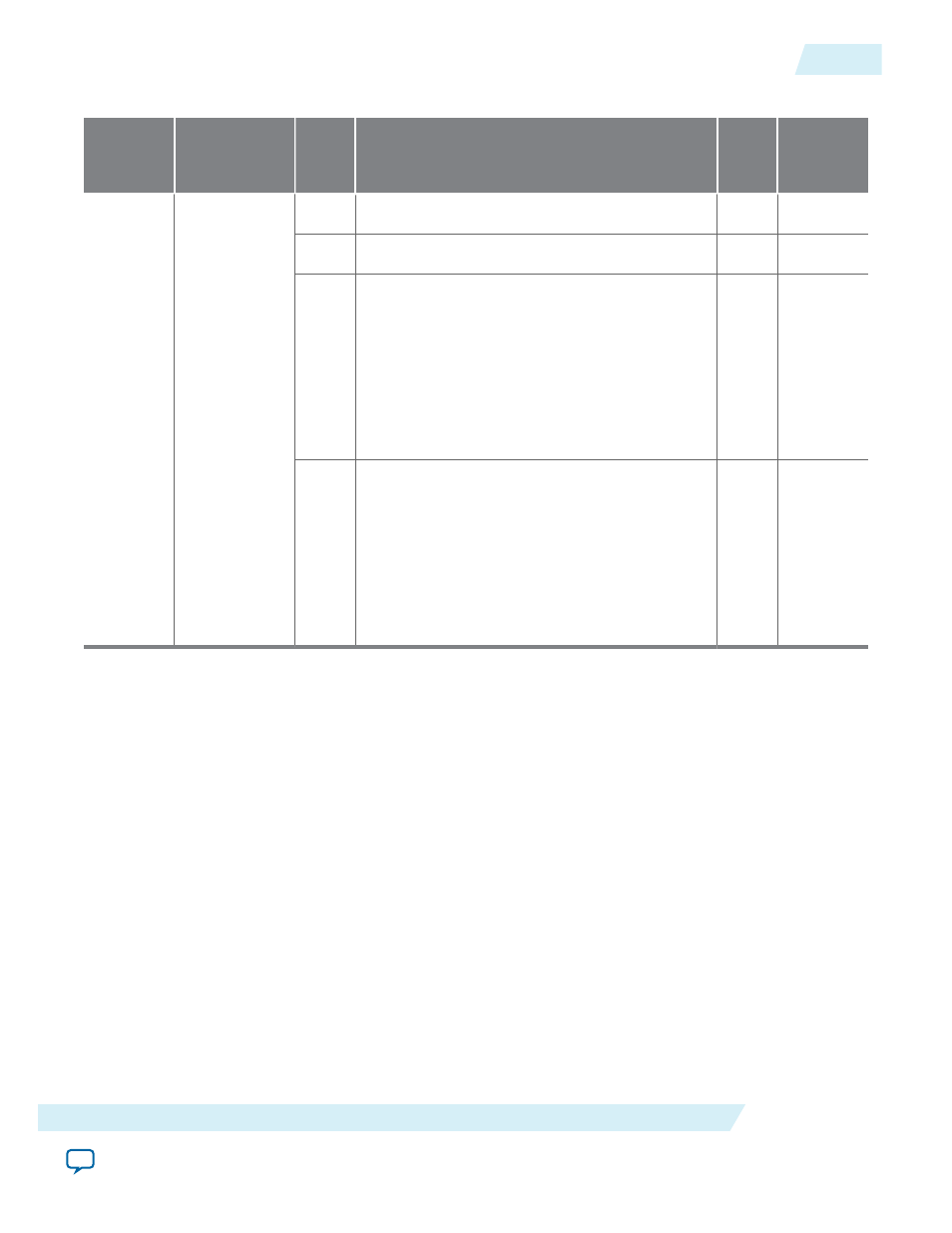

Table 3-35: Link Fault Signaling Configuration Register—Offset 0x122

Address

Name

Bit

Description

HW

Reset

Value

Access

0x122

MAC/RS link

fault

sequence

configuration

[5]

The remote fault status register.

1'b0

R

[4]

The local fault status register.

1'b0

R

[3:2]

The remote fault configuration register. Possible

configurations include:

• 2'b01: sends idle frames when remote fault is

received

• 2'b11: sends remote fault sequence when

remote fault is received

• 2'bx0: sends normal traffic when remote fault is

received

2'b00

RW

[1:0]

The local fault configuration register. Possible

configurations include:

• 2'b01: sends idle frames when local fault is

received

• 2'b11: sends remote fault sequence when local

fault is received

• 2'bx0: sends normal traffic when local fault is

received

2'b00

RW

Related Information

Link Fault Signaling Interface

Describes how the IP core uses the register values.

MAC and PHY Reset Registers

The following registers control the 40-100GbE MAC and PHY resets. Writing a 1’b1 to any of the reset

register fields initiates the corresponding reset sequence.

Note: Altera recommends that you reset the MAC and PHY using the following register reset sequence:

1. Write the value of 0x7 (all ones) to the PHY reset register at offset 0x1D.

2. Write the value of 0x3 (all ones) to the MAC reset register at offset 0x121.

3. Write the value of 0x0 (all zeros) to the MAC reset register at offset 0x121.

4. Write the value of 0x0 (all zeros) to the PHY reset register at offset 0x1D.

UG-01088

2014.12.15

MAC and PHY Reset Registers

3-89

Functional Description

Altera Corporation