Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 191

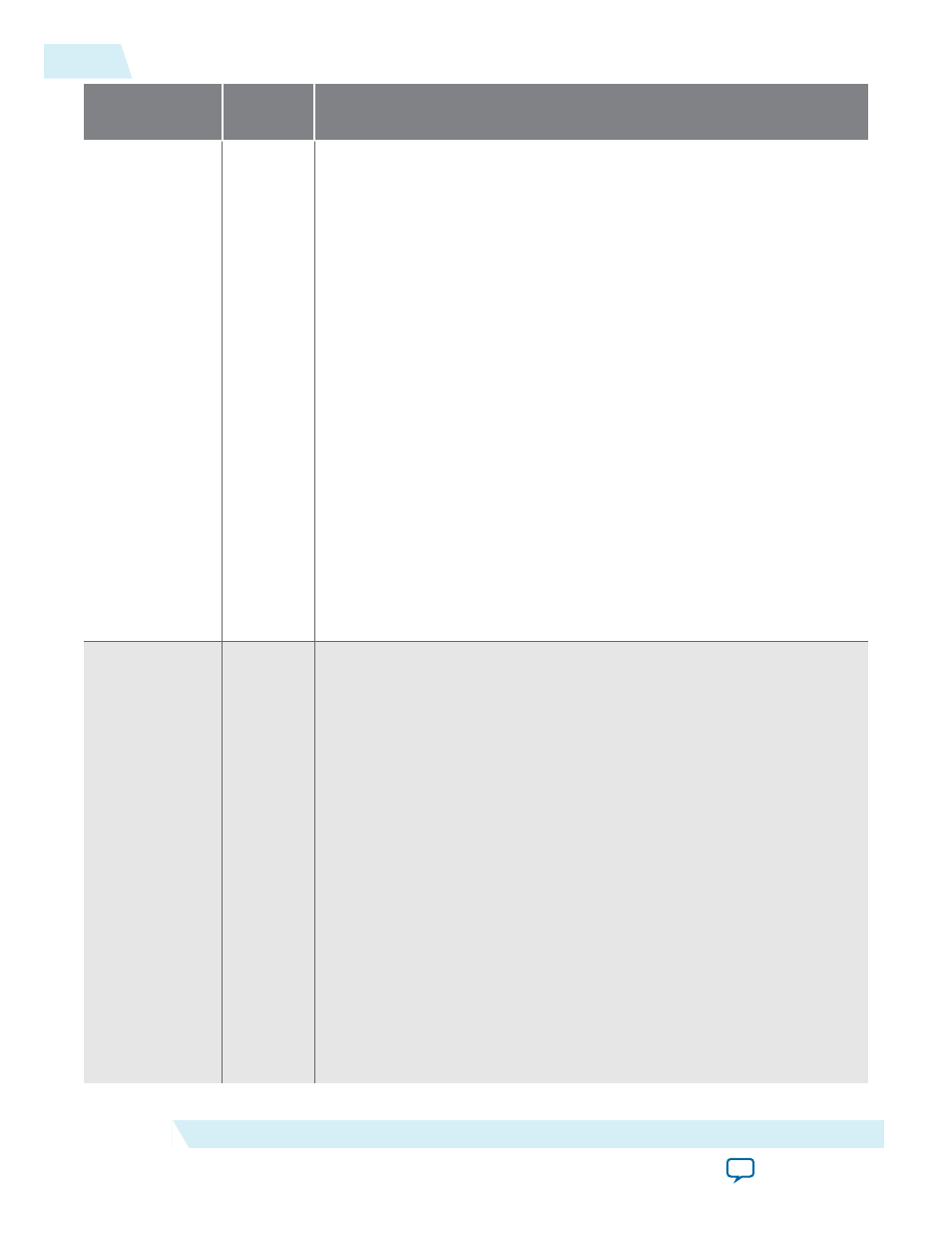

Date

ACDS

Version

Changes

• Added link to Low Latency 40-100GbE IP core user guide in

40- and 100-Gbps Ethernet MAC and PHY MegaCore Function

.

• Added new

appendix to provide the 10GBASE-

KR PHY register information that forms the basis for the

descriptions. This information is correct at the time of

.

• Removed mention of register 0x0C2 bit [8] from

on page 3-92 because this register bit is now described in the

10GBASE-KR PHY register listing.

• Clarified that the

tx_ready

signal might an inadequate indication that

the IP core is ready to accept and handle data on the TX client interface

with adapters. Following reset, the application should not send data on

this interface until after the

lanes_deskewed

signal is asserted,

indicating the IP core can safely transmit packets on the Ethernet link.

In the case of the TX client interface without adapters, the application

should also wait until after the

lanes_deskewed

signal is asserted.

Notice appears in

40-100GbE IP Core TX Data Bus with Adapters

and in

Without Adapters (Custom Streaming Interface)

• Corrected lists of testbench files in

. The new lists are correct for the IP core

v13.1 and later.

• Corrected assorted typos.

March 2014

v13.1

(2014.03.04

)

• Corrected device support list:

• To include support for Stratix V GS devices.

• To specify Final support for Stratix V devices.

• Included "40-100GbE IP Core TX Data Bus with Adapters (Avalon-ST

Interface)" section inadvertently omitted from previous version of user

guide.

• In "Frame Check Sequence (CRC-32) Insertion" section, corrected

CRC_

CONFIG

register bit that controls TX CRC insertion.

• Removed inconsistent statement in "40-100GbE IP core CRC Checking"

section that incorrectly indicated that CRC aligns with EOP.

• In "Statistics Counters Interface" section, fixed descriptions of the size-

based frame counting signals.

• In "Order of Transmission" section, improved figures showing byte

order on the Avalon-ST interface with and without preamble pass-

through enabled.

• In "About the 40- and 100-Gbps Ethernet MAC and PHY MegaCore

Function" chapter, removed mention of 4 and 20 virtual lanes, and

replaced with information correct for the Avalon-ST client-side

interface. The virtual lanes are relevant only on the Ethernet link.

• In "OpenCore Plus Time-Out Behavior" section, removed mention of

nonexistent

local_ready

signal.

D-2

40- and 100-Gbps Ethernet MAC and PHY MegaCore Function User Guide Revision

History

UG-01088

2014.12.15

Altera Corporation

Additional Information