Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 39

File Names

Description

run_vcs.sh

The Synopsys VCS script to run the testbench.

run_ncsim.sh

The Cadence NCSim script to run the testbench.

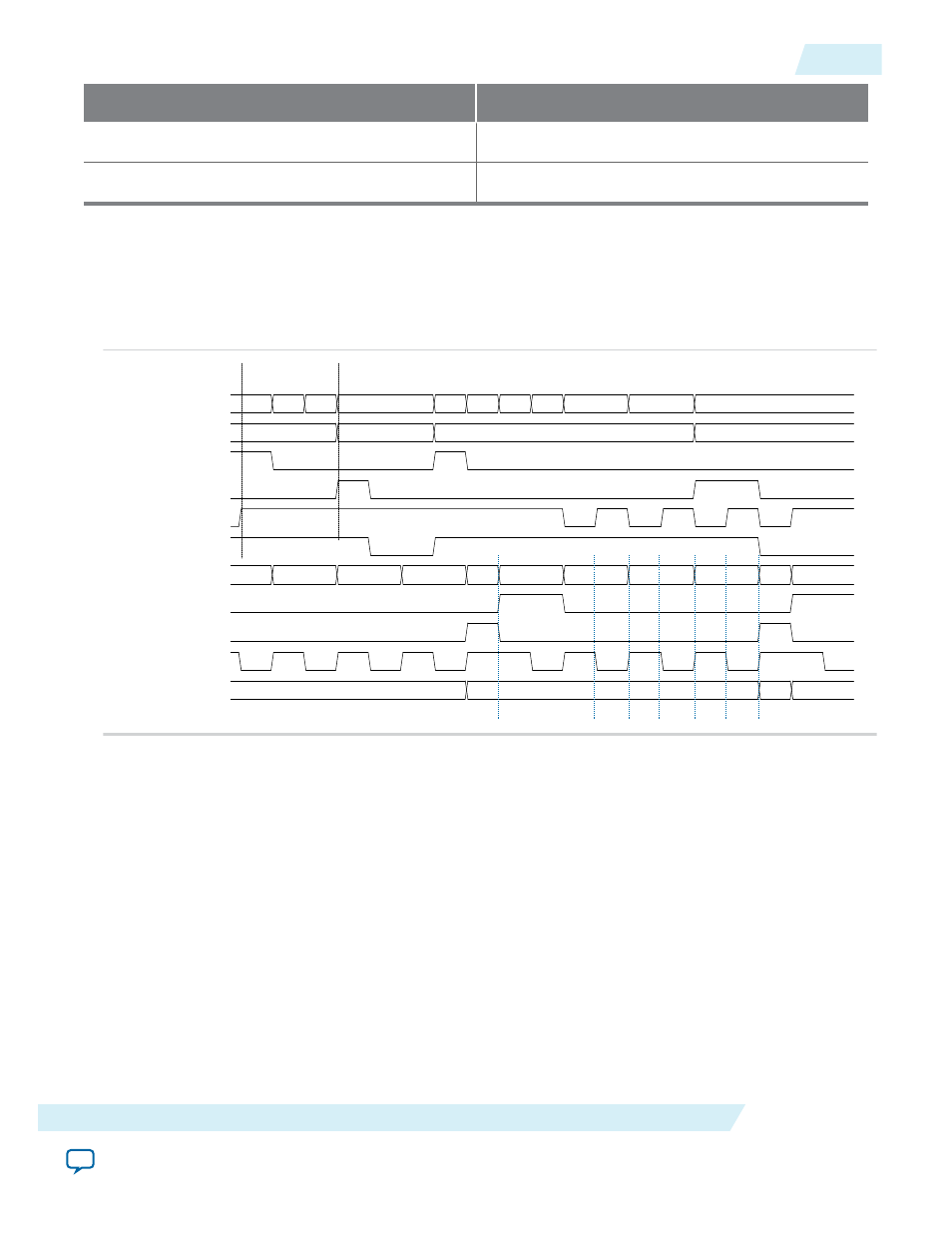

Figure 2-5: Typical 40GbE Traffic on the Avalon-ST Interface Using the Four- to Two-Word Adapters

Shows typical traffic from the simulation testbench created using the <instance_name>_example/

alt_e40_e100/example_testbench/run_vsim.do script in ModelSim.

Note: Client logic must maintain the

l4_tx_valid

signal asserted while asserting SOP, through the

assertion of EOP. Client logic should not pull this signal low during a packet transmission.

l4_tx_data[255:0]

l4_tx_empty[4:0]

l4_tx_startofpacket

l4_tx_endofpacket

l4_tx_ready

l4_tx_valid

l4_rx_data[255:0]

l4_rx_startofpacket

l4_rx_endofpacket

l4_rx_valid

l4_rx_empty[4:0]

B8 . B8 . B8 . B87B0031B8

. 57 . 57 . 57 . 57 . 573500

. 5735004

. 57350055573500545735005357

00

02

00

01

65F300 .. 65F301

. 65F301

. 65F301

. FA . FAAB00

. FAAB00

. FAAB00

. FAAB00

. 61 . 61A000

.

14

1D

1

2

3

4

6

8

9

7

5

The markers in the figure show the following sequence of events:

1. At marker 1, the application asserts

l4_tx_startofpacket

, indicating the beginning of a TX packet.

2. At marker 2, the application asserts

l4_tx_endofpacket

, indicating the end of the TX packet. The

value on

l4_tx_empty[4:0]

indicates that the 2 least significant bytes of the last data cycle are empty.

3. At marker 3, the IP core asserts

l4_rx_startofpacket

, indicating the beginning of an RX packet. A

second transfer has already started on the TX bus.

4. At marker 4, the 40GbE IP core deasserts

l4_rx_valid

, indicating that the IP core does not have new

valid data to send to the client on

l4_rx_data[255:0]

.

l4_rx_data[255:0]

remains valid and

unchanged for a second cycle.

5. A marker 5, the 40GbE IP core asserts

l4_rx_valid

, indicating that the it has valid data to send to the

client on

l4_rx_data[255:0]

.

6. At marker 6, the 40GbE IP core deasserts

l4_rx_valid

, indicating that it does not have new valid data

to send to the client on

l4_rx_data[255:0]

.

l4_rx_data[255:0]

remains unchanged for a second

cycle.

UG-01088

2014.12.15

Testbenches with Adapters

2-17

Getting Started

Altera Corporation