Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 192

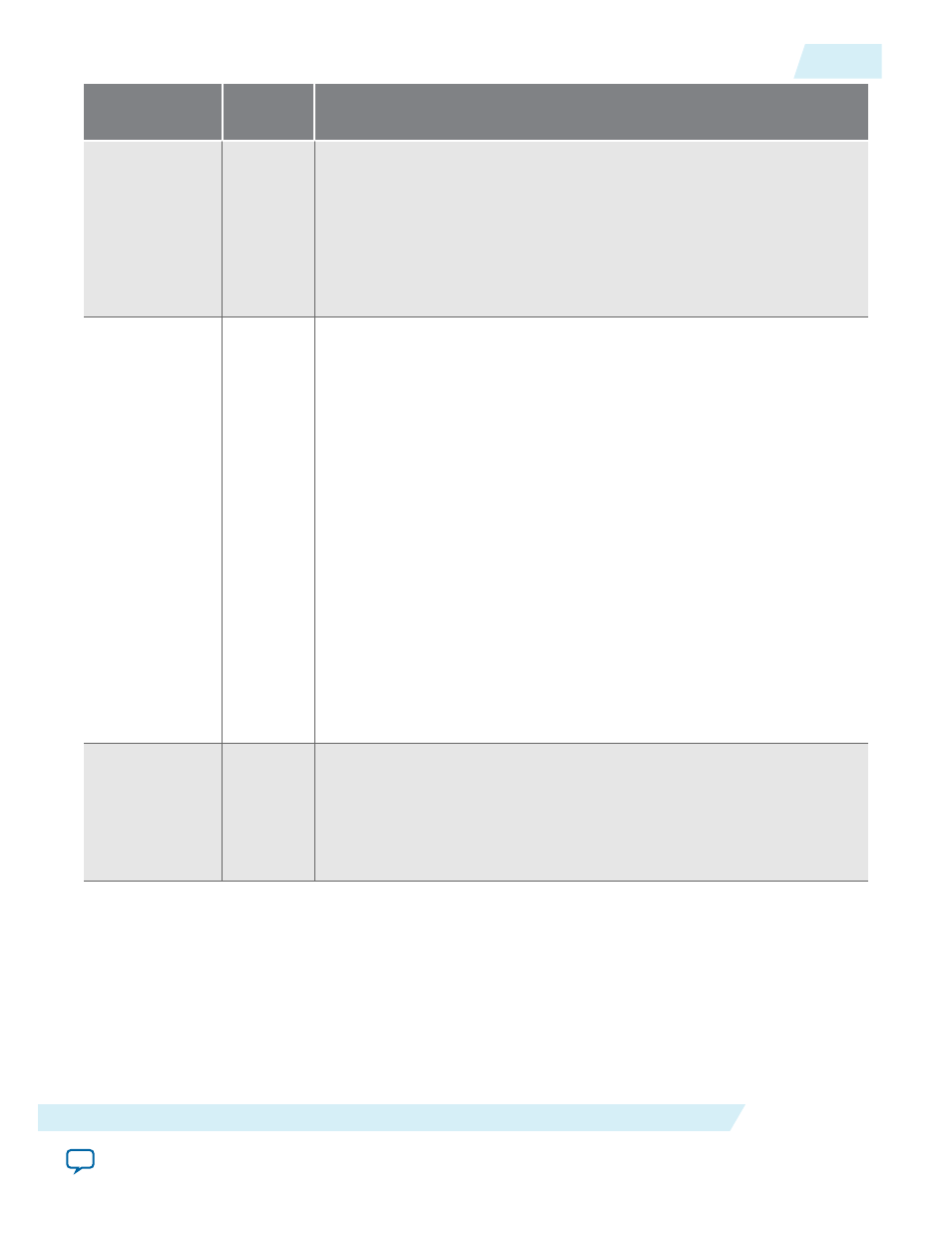

Date

ACDS

Version

Changes

• In "Simulating the 40-100GbE IP Core with the Testbenches" section,

removed option to include or exclude waveform generation in the

simulation scripts. The scripts do include this option in pre-13.1

releases.

• Corrected topics to include links to both internal (other sections) and

external (other documents and websites). Previously only one or the

other appeared in each section in the document.

• Fixed assorted typos.

November

2013

v13.1

(2013.11.04

)

• Added new 40GBASE-KR4 support with FEC option, including new

parameters, signals, registers, testbench, and example design.

• Added new parameter for Synchronous Ethernet support option to

separate the reference input clocks for the RX CDR PLL and the TX PLL

and make the RX recovered clock visible.

• Added the following new signals:

• Link fault signals visible in duplex variations:

remote_fault_status

and

local_fault_status

.

• PHY status signals visible in MAC+PHY variations:

tx_lanes_

stable

and

lanes_deskewed

.

• New clock signals for SyncE variations:

rx_clk_ref

,

tx_clk_ref

,

and

rx_recovered_clk

.

• New 40GBASE-KR4 signals for analog reconfiguration.

• Updated testbench descriptions to describe the new streamlined

testbenches and the new 40GBASE-KR4 example design and testbench.

• Updated descriptions of testbenches and example designs to clarify the

user no longer needs to configure the DUT with a specific name and

clock rate.

• Updated resource utilization numbers.

• Corrected module names in 40GbE IP core resource utilization tables.

July 2013

1.3(v13.0)

• Corrected signal widths and descriptions in Figure 3-2 on page 3-2 and

Figure 3-3 on page 3-3.

• Corrected Avalon-ST client interface signal widths in Figure 3-5 on page

3-8, Table 3-2 on page 3-8, Figure 3-20 on page 3-23, and Table 3-6 on

page 3-23.

• Renamed and reorganized "Signals" on page 3-40.

UG-01088

2014.12.15

40- and 100-Gbps Ethernet MAC and PHY MegaCore Function User Guide Revision

History

D-3

Additional Information

Altera Corporation