Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 55

Signal Name

Direction

Description

l<n>_tx_ready

Output

When asserted, the MAC is ready to receive data. The

l<n>_tx_ready

signal acts as an acknowledge. The source

drives

l<n>_tx_valid

and

l<n>_tx_data[<n>*64-1:0]

,

then waits for the sink to assert

l<n>_tx_ready

. The

readyLatency

is zero cycles, so that the IP core accepts

valid data in the same cycle in which it asserts

l<n>_tx_

ready

.

The

tx_ready

signal indicates the MAC is ready to receive

data in normal operational model. However, the

tx_ready

signal might not be an adequate indication following reset.

To avoid sending packets before the Ethernet link is able

to transmit them reliably, you should ensure that the

application does not send packets on the TX client

interface until after the

lanes_deskewed

signal is asserted.

l<n>_tx_valid

Input

When asserted

l<n>_tx_data

is valid. This signal must be

continuously asserted between the assertions of

l<n>_tx_

startofpacket

and

l<n>_tx_endofpacket

for the same

packet.

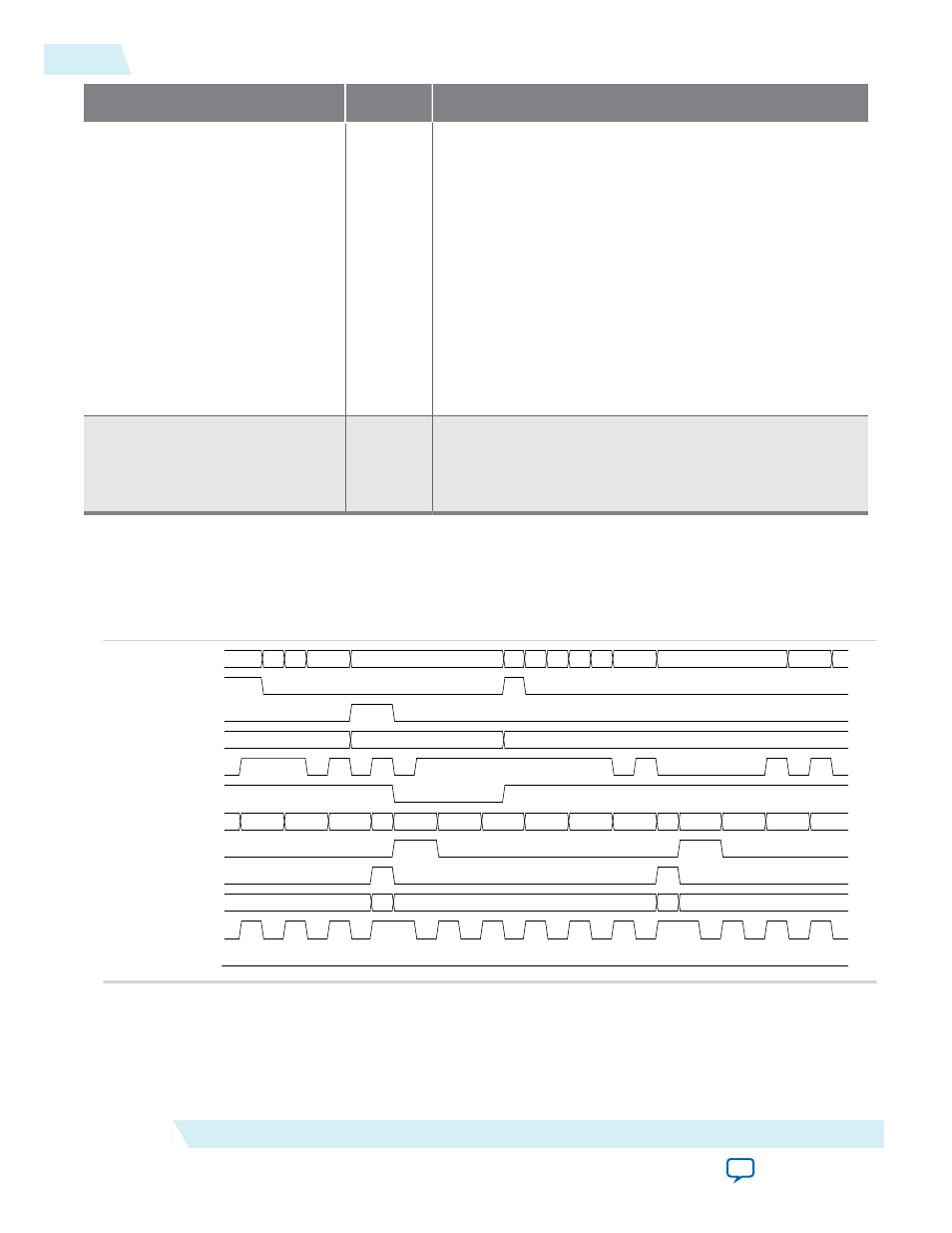

Figure 3-4: Traffic on the TX and RX Client Interface for 40GbE IP Core Using the Four- to Two-Word

Adapters

Shows typical traffic for the TX and RX Avalon-ST interface 40GbE IP core. This example shows a part of

a ModelSim simulation of the parallel testbench provided with the IP core.

l4_tx_data[255:0]

l4_tx_startofpacket

l4_tx_endofpacket

l4_tx_empty[4:0]

l4_tx_ready

l4_tx_valid

l4_rx_data[255:0]

l4_rx_startofpacket

l4_rx_endofpacket

l4_rx_empty[4:0]

l4_rx_valid

l4_rx_error

2 . 2 . 2 . 2C83 . 2C8300392C8300382C

. 3 . 3 . 3 . 3 . 3 . 3EF9 . 3EF900553EF90054

. 3EF9 . 3EF9

00

0D

00

.. 7B44 . 7B44 . 7B44 . E . EFB8 . EFB8 . EFB8 . EFB8 . EFB8 . EFB8 . E . EAD . EAD2 . EAD2 . EAD

.

1E

02

1A

3-8

40-100GbE IP Core TX Data Bus with Adapters (Avalon-ST Interface)

UG-01088

2014.12.15

Altera Corporation

Functional Description