Lock status registers – Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 131

Lock Status Registers

The following registers show the lock status of the high speed I/O and RX PCS.

RX_AGGREGATE[0]

aggregates the status of the individual RX PCS channels. When this bit is set to 1, the RX PCS is operating

normally. When this bit is set to 0, the other information indicates the cause.

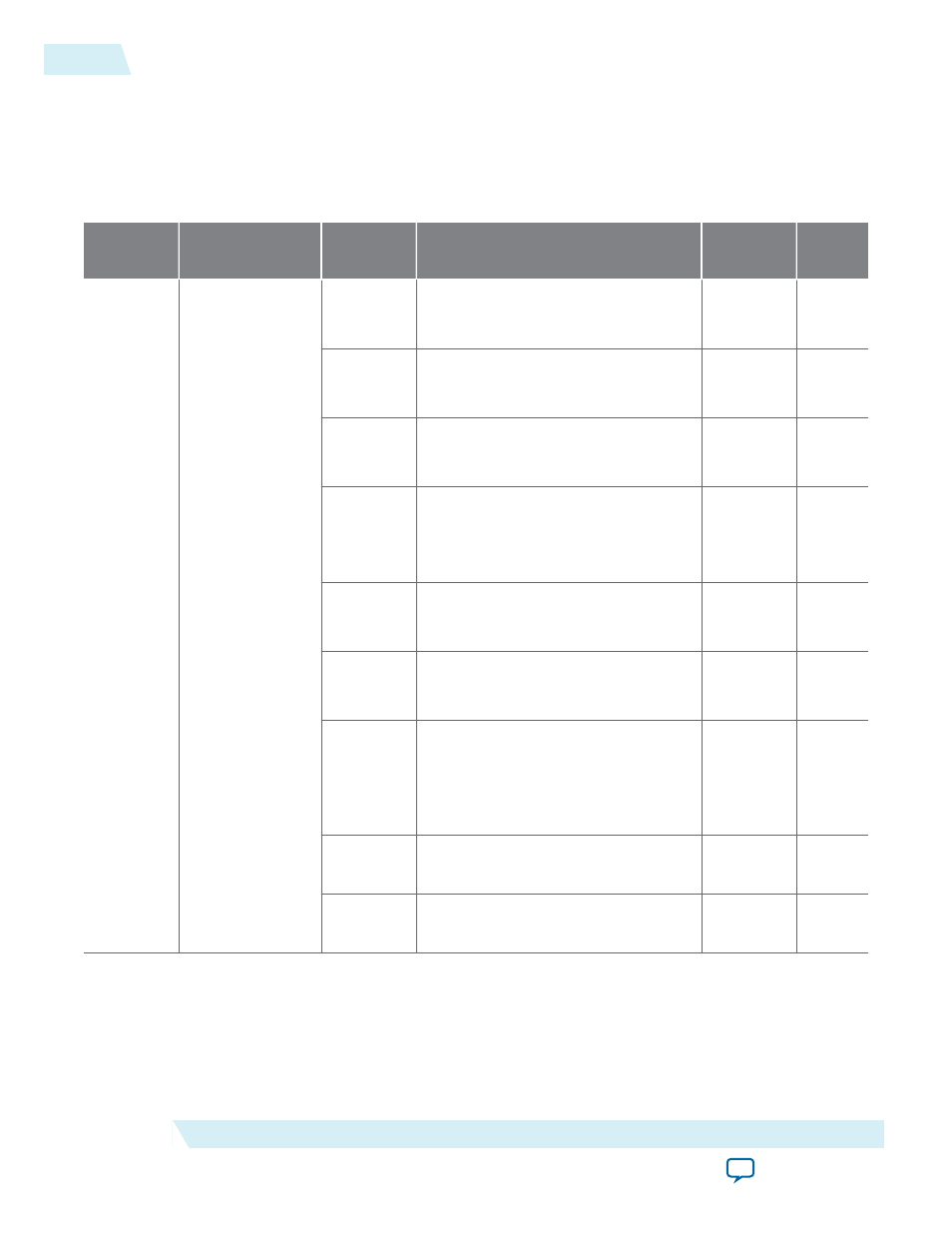

Table 3-28: Lock Status Registers

Address

Name

Bit

Description

HW Reset

Value

Access

0x010

IO_LOCKS

For all

options except the

CAUI-4 configu‐

ration.

[31:25]

(100 GbE)

Reserved.

0x7f

R

[24:22]

(100 GbE)

When asserted, indicates that the

corresponding TX PLL is locked.

0x0

R

[21:12]

(100 GbE)

Reserved.

0x3ff

R

[11:2]

(100 GbE)

When asserted, indicates that the

corresponding RX CDR locked. The

lowest bit corresponds to lane 0 and so

forth.

0x0

R

[31:7]

(40 GbE)

Reserved.

0x1ffffff

R

[6]

(40 GbE)

When asserted, indicates that the TX

PLL is locked.

1’b0

R

[5:2]

(40 GbE)

When asserted, indicates that the

corresponding RX CDR is locked. Bit 2

corresponds to lane 1, bit 3 corresponds

to lane 2, bit 4 corresponds to lane 3,

and bit 5 corresponds to lane 4.

0x0

R

[1]

When asserted, indicates that the TX

interface is ready.

1’b0

R

[0]

When asserted, indicates that the RX

interface is ready.

1’b0

R

3-84

Lock Status Registers

UG-01088

2014.12.15

Altera Corporation

Functional Description