Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 170

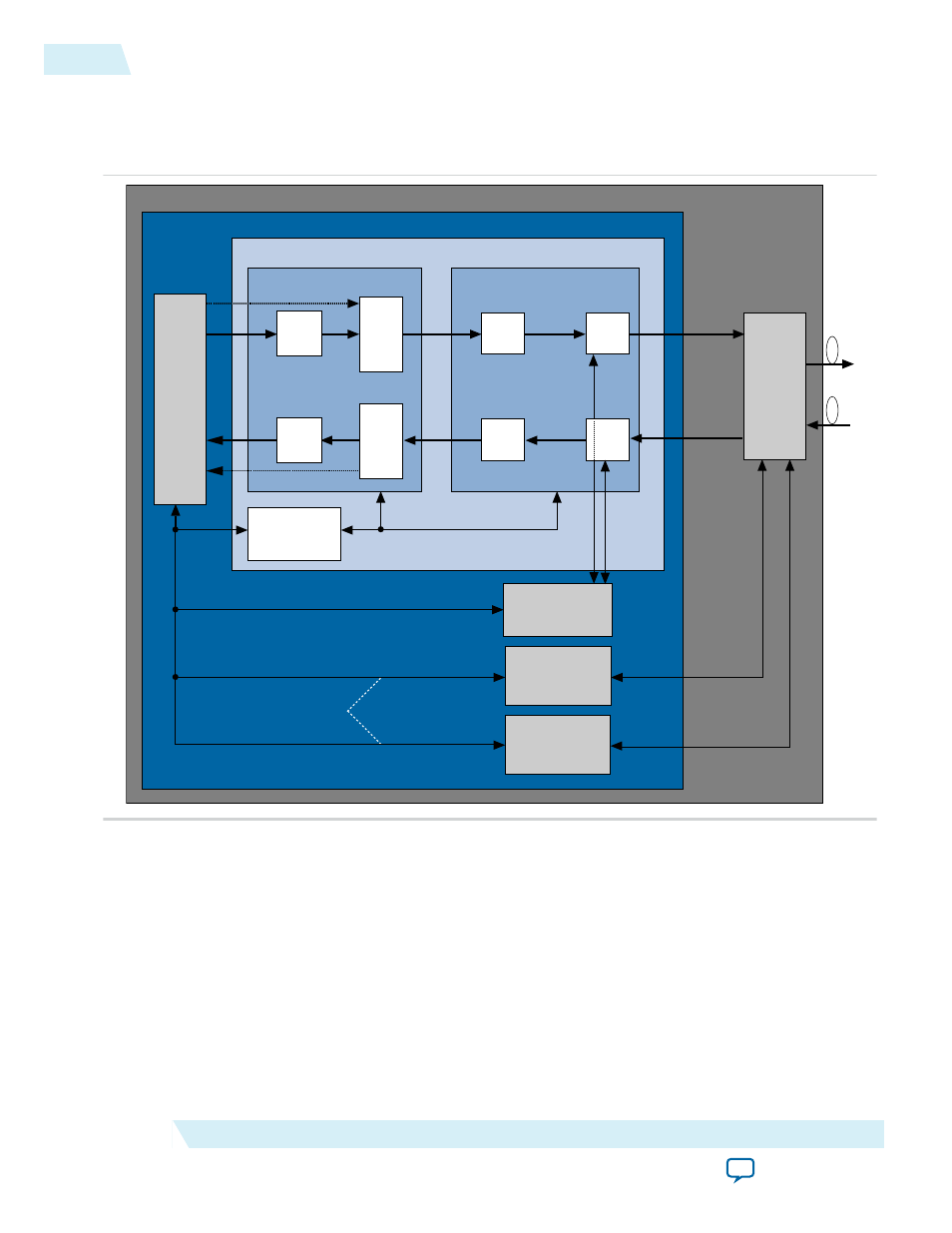

Figure A-1: High Level Block Diagram for the 40-100GbE Example Design

High level block diagram for non-40GBASE-KR4 example designs. You can generate a non-40GBASE-

KR4 example design for any non-40GBASE-KR4, full duplex IP core variation that includes both MAC

and PHY components.

40- or 100-Gbps Ethernet MAC and PHY MegaCore Function

40- or 100-Gbps Ethernet Example Design

Altera FPGA

Client

Logic

TX

FIFO

TX

MAC

RX

MAC

40- and 100-GbE MAC

PMA

PMA

PCS

Transceiver PHY

TX

Adapter

PCS

XLGMII w/data_valid signal

or CGMII w/data_valid signal

4 x 40 bits or

10 x 40 bits

XLAUI: 4 x 10.3125 Gbps or

CAUI: 10 x 10.3125 Gbps

Custom Streaming

Avalon-ST

Avalon-ST

PMD

Optical

Module

CFP

or

QSFP

Control and

Status Interface

Avalon-MM

Management Interface

MDIO (CFP)

or

2 Wire Serial (QSFP)

PMD

Controller

RX

Adapter

Custom Streaming

Reconfiguration

Controller (Arria V GZ

and Stratix V only)

A-2

40-100GbE IP Core Example Design

UG-01088

2014.12.15

Altera Corporation

40-100GbE IP Core Example Design