Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 73

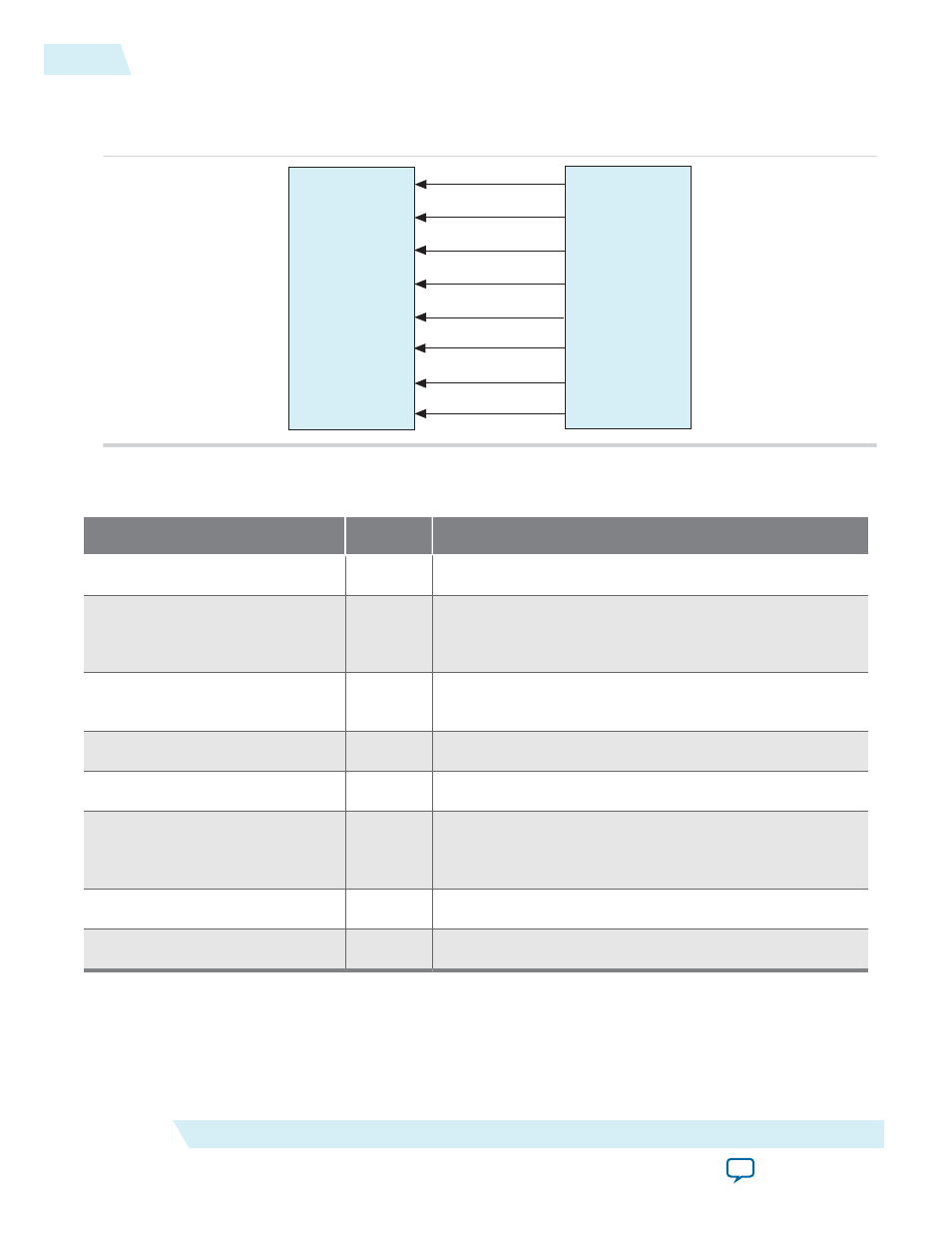

Figure 3-22: RX MAC to Client Interface with Adapters

The Avalon-ST interface bus width varies with the IP core variation. In the figure, <n> = 4 for the 40GbE

IP core and <n> = 8 for the 100GbE IP core. <l> is log

2

(8*<n>).

l<n>_rx_data[<n>*64-1:0]

l<n>_rx_empty[<l>-1:0]

l<n>_rx_startofpacket

l<n>_rx_endofpacket

l<n>_rx_error

l<n>_rx_valid

l<n>_rx_fcs_valid

l<n>_rx_fcs_error

RX

Client

RX

MAC

Table 3-5: Signals of the RX Client Interface with Adapters

In the table, <n> = 4 for the 40GbE IP core and <n> = 8 for the 100GbE IP core. <l> is log

2

(8*<n>).

Name

Direction

Description

l<n>_rx_data[<n>*64-1:0]

Output

RX data.

l<n>_rx_empty[<l>-1:0]

Output

Indicates the number of empty bytes on

l<n>_rx_data

when

l<n>_rx_endofpacket

is asserted, starting from the

least significant byte (LSB).

l<n>_rx_startofpacket

Output

When asserted, indicates the start of a packet. The packet

starts on the MSB.

l<n>_rx_endofpacket

Output

When asserted, indicates the end of packet.

l<n>_rx_error

Output

When asserted indicates an error condition.

l<n>_rx_valid

Output

When asserted, indicates that RX data is valid. Only valid

between the

l<n>_rx_startofpacket

and

l<n>_rx_

endofpacket

signals.

l<n>_rx_fcs valid

Output

When asserted, indicates that FCS is valid.

l<n>_rx_fcs_error

Output

When asserted, indicates an FCS error condition.

3-26

40-100GbE IP Core RX Data Bus with Adapters (Avalon-ST Interface)

UG-01088

2014.12.15

Altera Corporation

Functional Description