Altera 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 109

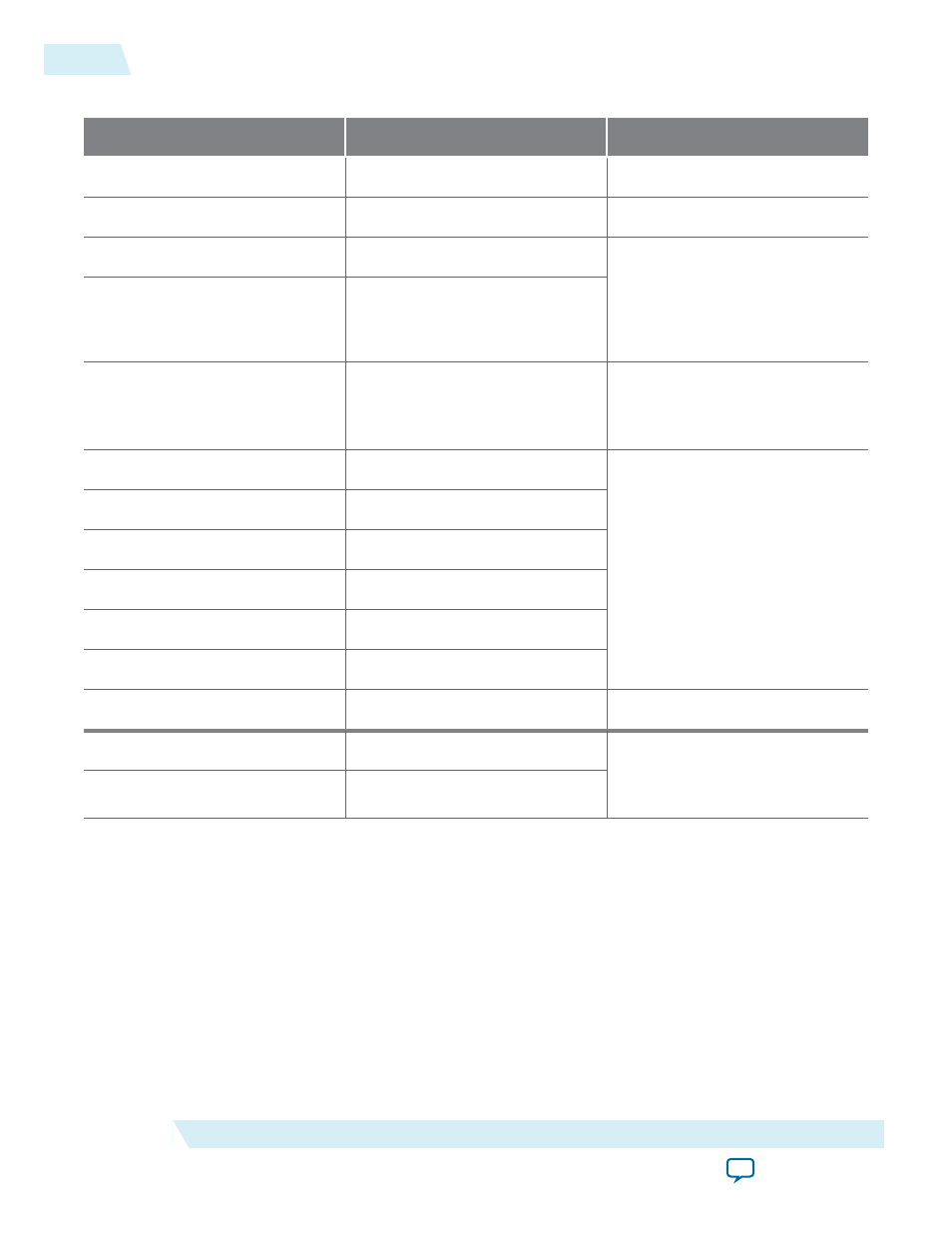

Table 3-20: 40-100GbE MAC and PHY IP Core Without Adapters: Common Signals

Signal Name

Direction

Description

pma_arst_ST

Input

Resets

clk_ref

Input

Clocks

tx_clk_ref

Input

Clocks

In Sync–E variations, these two

clock signals replace

clk_ref

.

All Sync–E variations are duplex

IP cores.

rx_clk_ref

Input

rx_recovered_clk

Output

Clocks

This signal is present only in

Sync-E variations.

status_addr[15:0]

Input

Control and status interface

status_read

Input

status_write

Input

status_writedata[31:0]

Input

status_readdata[31:0]

Output

status_readdata_valid

Output

clk_status

Input

Clocks

remote_fault_status

Output

Link fault signaling interface

These two signals are available

only in duplex variations.

local_fault_status

Output

3-62

Signals of MAC and PHY Variations Without Adapters

UG-01088

2014.12.15

Altera Corporation

Functional Description