Altera PCI Compiler User Manual

Page 104

3–30

User Guide Version 11.1

Altera Corporation

PCI Compiler

October 2011

Configuration Registers

device ID register value on the Read-Only PCI Configuration Registers

page. The specified default state is defined as the state of the register

when the PCI bus is reset.

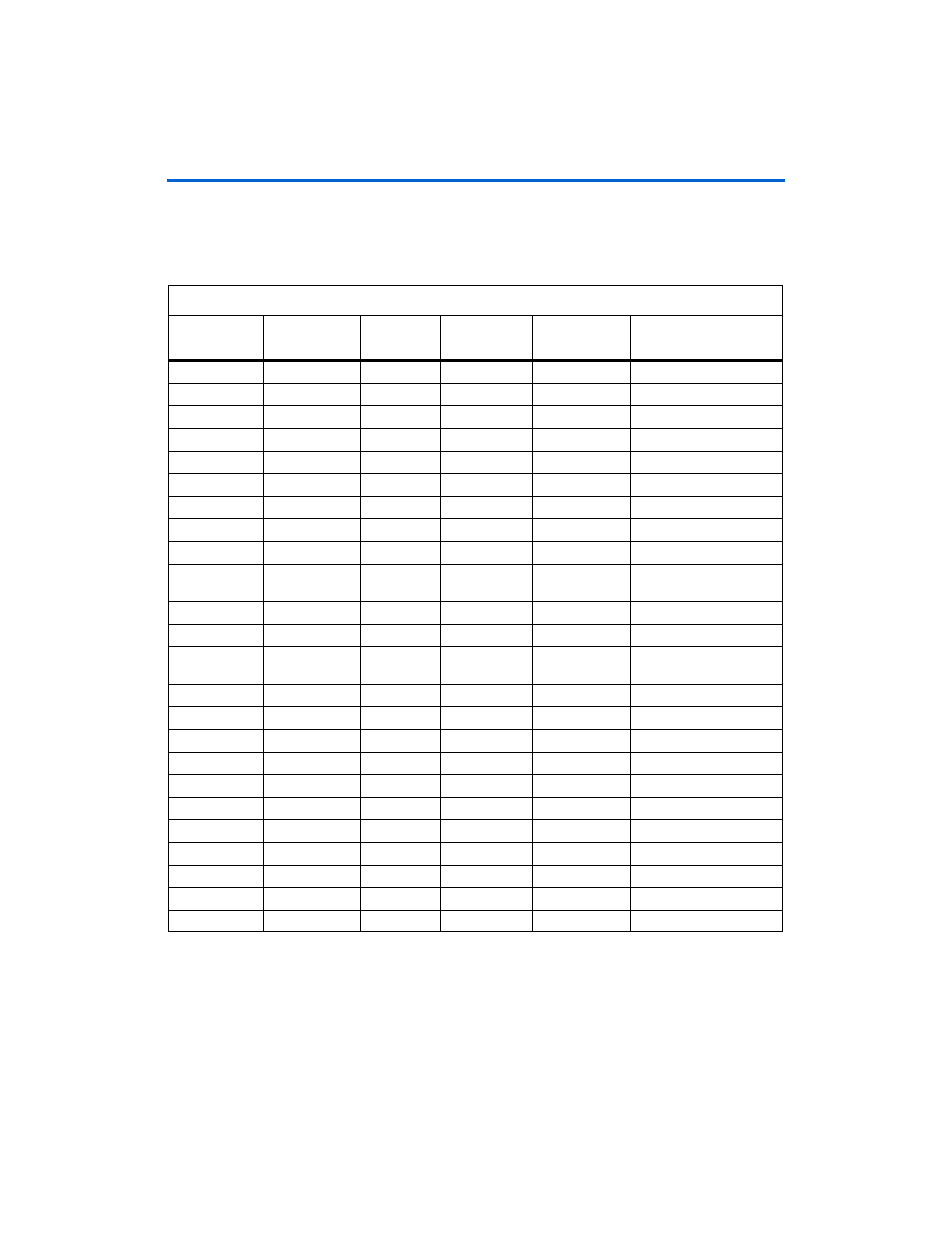

Table 3–13. Supported Configuration Registers Address Map

Address Offset

Range

Reserved

Bytes Used/

Reserved

Read/Write

Mnemonic

Register Name

0x00

0x00-0x01

2/2

Read

ven_id

Vendor ID

0x02

0x02-0x03

2/2

Read

dev_id

Device ID

0x04

0x04-0x05

2/2

Read/write

comd

Command

0x06

0x06-0x07

2/2

Read/write

status

Status

0x08

0x08-0x08

1/1

Read

rev_id

Revision ID

0x09

0x09-0x0B

3/3

Read

class

Class code

0x0C

0x0C-0x0C

1/1

Read/write

cache

0x0D

0x0D-0x0D

1/1

Read/write

lat_tmr

Latency timer

0x0E

0x0E-0x0E

1/1

Read

header

Header type

0x10

0x10-0x13

4/4

Read/write

bar0

Base address register

zero

0x14

0x14-0x17

4/4

Read/write

bar1

Base address register one

0x18

0x18-0x1B

4/4

Read/write

bar2

Base address register two

0x1C

0x1C-0x1F

4/4

Read/write

bar3

Base address register

three

0x20

0x20-0x23

4/4

Read/write

bar4

Base address register four

0x24

0x24-0x27

4/4

Read/write

bar5

Base address register five

0x28

0x28-0x2B

4/4

Read

cardbus_ptr

CardBus CIS pointer

0x2C

0x2C-0x2D

2/2

Read

sub_ven_id

Subsystem vendor ID

0x2E

0x2E-0x2F

2/2

Read

sub_id

Subsystem ID

0x30

0x30-0x33

4/4

Read/write

exp_rom_bar

Expansion ROM BAR

0x34

0x34-0x35

1/1

Read

cap_ptr

Capabilities pointer

0x3C

0x3C-0x3C

1/1

Read/write

int_ln

Interrupt line

0x3D

0x3D-0x3D

1/1

Read

int_pin

Interrupt pin

0x3E

0x3E-0x3E

1/1

Read

min_gnt

Minimum grant

0x3F

0x3F-0x3F

1/1

Read

max_lat

Maximum latency

Note to

:

(1)

These registers are supported by the pci_mt64 and pci_mt32 MegaCore functions only.