Altera PCI Compiler User Manual

Page 304

7–36

User Guide Version 11.1

Altera Corporation

PCI Compiler

October 2011

PCI Master Operation

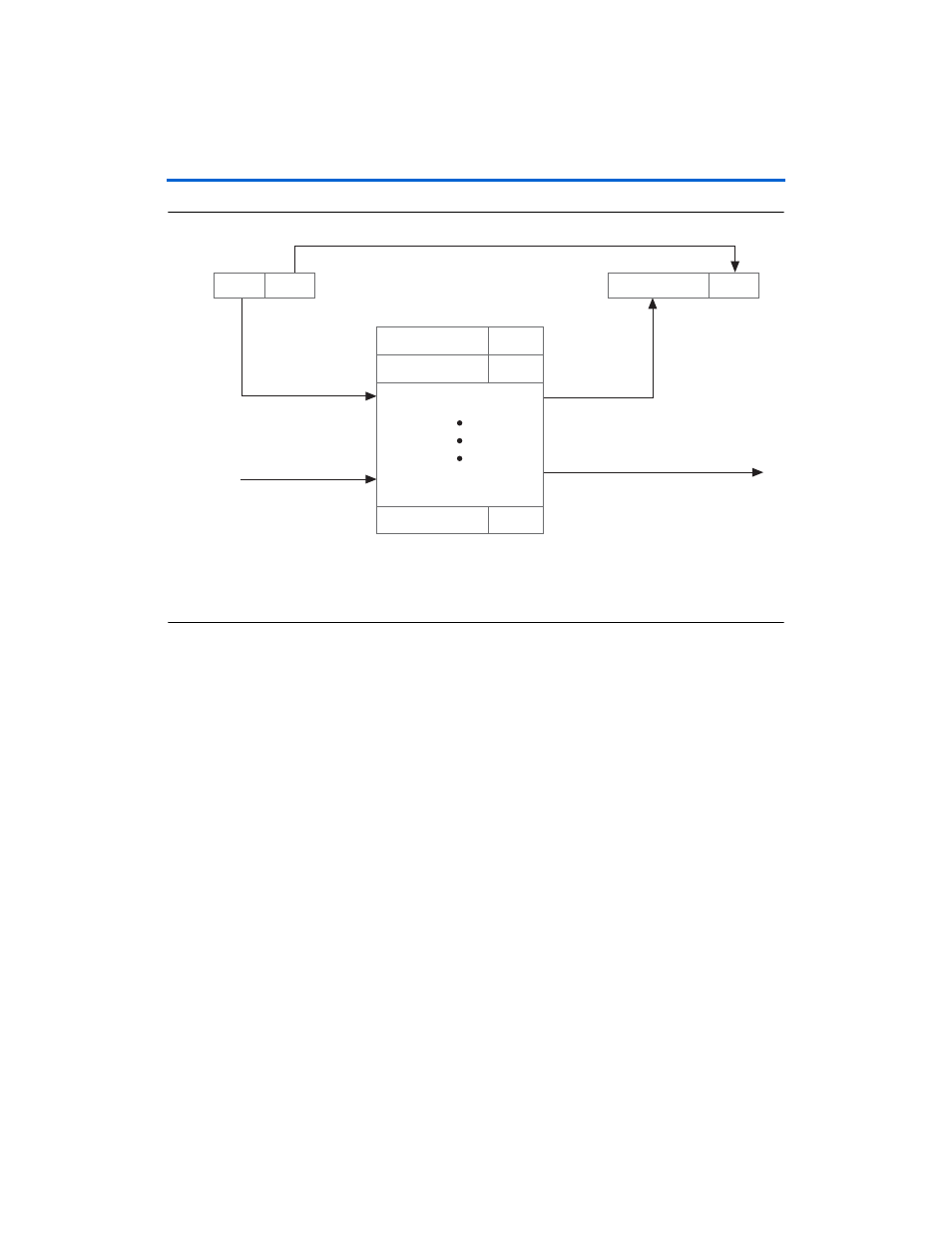

Figure 7–10. Avalon-to-PCI Address Translation

Address Translation Table Size (refer to

) selections determine both the number of entries in the

Avalon-to-PCI address translation table, and the number of bits that are

passed through the transaction table unchanged.

Each entry in the address translation table also has two address space

indication bits, which specify the type of address space being mapped. If

the type of address space being mapped is memory, the bits also indicate

Avalon Address

PCI Address

High

Low

N = Number of Pass Through Bits

M = Number of Avalon Address Bits

P = Number of PCI Address Bits

Q = Number of Translation Table Entries

Sp = Space Indication for Each Entry

Low Address Bits Unchanged

Avalon to PCI Address

Translation Table

(Q Entries by P-N Bits wide)

PCI Address from Table Entry

Used as High PCI Address Bits

Space Indication

Table Updates via

Control Register Port

High Avalon Address

Bits Index Table

PCI Address 0

Sp0

PCI Address 1

Sp1

PCI Address Q-1

SpQ-1

0

N-1

M-1

N

High

Low

0

P-1

N N-1